Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024 5 series Cell Li-ion Rechargeable Battery Protection IC with cell balancing function

#### General Description

The ML5206 is a protection IC with cell balancing function for the 3- to 5-cell Li-ion rechargeable battery pack. It detects individual cell overvoltage and battery cell open-wire, and alerts by alarm output signal. And cell balancing function is built in and it is automatically executed.

#### Features

- 3 to 5 cell high precision overvoltage detection function Overvoltage detection threshold  $V_{OV}$ : 4.0V to 4.4V (5mV step), error:  $\pm 25mV$  (0°C to 60°C) Overvoltage release threshold  $V_{OVR}$  : VOV - 0 to 200mV (10mV step) error:  $\pm 25$ mV to 35mV (0°C to 60°C) Overvoltage detection delay time :  $0 \sec to 5.6 \sec(typ)$ • Open-wire detection function Open-wire detection threshold : 0.6V(typ) Open-wire detection sink current : 100nA(typ) Open-wire detection delay time : 0sec to 5.6sec(typ) • Cell balancing function Cell balancing detection threshold V<sub>CB</sub> : 4.0V to 4.4V (5mV step), error:  $\pm 25$ mV (0°C to 60°C) Cell balancing relase threshold  $V_{CBR}$  : VCB - 0 to 200mV (10mV step), error:  $\pm 25$ mV ot 35mV (0°C to 60°C) Cell balancing current : 40 mA(typ)Cell balancing detection delay time : 0sec to 5.6sec(typ)

- 3 types of alarm output Selected from CMOS / Nch open drain / Pch open drain

- Setting number of connected battery cells : defined with part-number 5 cells = ML5206-001, 4 cells =ML5206-001A, 3 cells=ML5206-001B

- Low current consumption  $1\mu A(typ), 2\mu A(max) (0^{\circ}C to 60^{\circ}C)$

- Power supply voltage :+5V to +25V

- Operating temperature : -20°C to +85°C

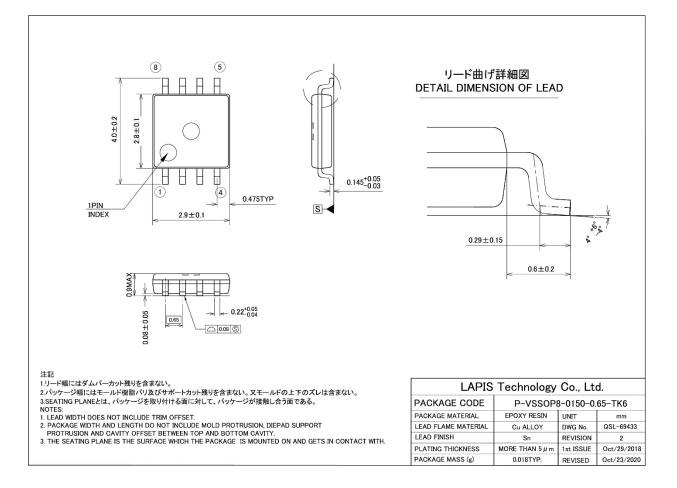

- Package : 8 pin VSSOP

Application

•Power tools and Garden tools

•Cordless Cleaner

#### Part number

ML5206-001MB 5 cells, Nch open drain output ML5206-001BMB 3 cells, Nch open drain output The detection voltage, etc., is the same for both 5 cells and 3 cells.

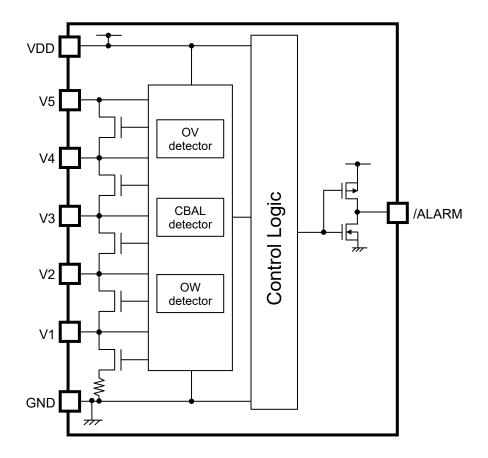

Block Diagram

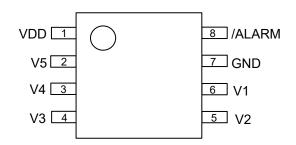

■ Pin Configuration (top view)

| Pin No. | Pin    | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | VDD    | _   | Power supply input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 2       | V5     | Ι   | Battery cell 5 high voltage input pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 3       | V4     | Ι   | Battery cell 5 low voltage input and Battery cell 4 high voltage input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4       | V3     | I   | Battery cell 4 low voltage input and Battery cell 3 high voltage input pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 5       | V2     | Ι   | Battery cell 3 low voltage input and Battery cell 2 high voltage input pin.<br>Should be connected to GND for the 3 cell series connected battery pack application.                                                                                                                                                                                                                                                                                                                                                                                      |

| 6       | V1     | Ι   | Battery cell 2 low voltage input and Battery cell 1 high voltage input pin.<br>Should be connected to GND for the 3 or 4 cell series connected battery pack application.                                                                                                                                                                                                                                                                                                                                                                                 |

| 7       | GND    | —   | Ground pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 8       | /ALARM | 0   | Alarm signal output pin.<br>•If CMOS output : Output level is "L" level(GND level) if overvoltage/ open-wire is<br>detected, else "H" level (VDD power supply level). Its reversed setting is possible.<br>•If Nch open drain output : Output level is "L" level(GND level) if overvoltage/<br>open-wire is detected, else "Hi-Z" level. Its reversed setting is possible.<br>•If Pch open drain output: Output level is "H"level (VDD power supply level) if<br>overvoltage/open-wire is detected, else "Hi-Z" level. Its reversed setting is possible. |

#### Pin Description

#### Absolute Maximum Ratings

(GND= 0 V, Ta = 25 °C) Symbol Condition Rating Item Unit Supply Voltage Vdd Applied to VDD pin -0.3 to +33 V Applied to V5 to V1 pins Vn+1 -Vn pin voltage defference -0.3 to +6.5 V  $V_{IN}$ (note1) V1 – GND pin voltage difference Input Voltage Applied to between V2-V1 pins. VIN2 When cell balancing switch between -0.3 to +7.5 V V2-V1 pins is OFF. Applied to V5 pin  $V_{\text{IN5}}$ -0.3 to + VDD + 6.5 V Applied to /ALARM pin (CMOS, Pch V Vout1 -0.3 to V<sub>DD</sub>+0.3 open-drain) **Output Voltage** Applied to /ALARM pin (Nch V Vout2 -0.3 to +32 open-drain) Cell balancing Per every cellbalancing switch lсв 100 mΑ current Short-circuit Applied to /ALARM pin los 10 mΑ output current Mounted on the JEDEC 4-layer Power dissipation  $P_{D}$ 730 mW board Storage -55 to +150 °C TSTG temperature

(note 1) When connecting or disconnecting battery cells, the voltage difference between  $V_{n+1}$ .  $V_n$  pins might exceed this ratings and the LSI will be destructed.

#### Recommended Operating Conditions

(GND=0V)

| Item                  | Symbol | Condition | Range      | Unit |

|-----------------------|--------|-----------|------------|------|

| Supply Voltage        | Vdd    | _         | 5 to 25    | V    |

| Operating temperature | TOP    | _         | -20 to +85 | °C   |

# Electrical Characteristics

• DC Characteristics

|                        |                  |                            | V <sub>DD</sub> =5 t | o 25V, GND= | =0 V, Ta=-20    | to +85°C |  |

|------------------------|------------------|----------------------------|----------------------|-------------|-----------------|----------|--|

| Item                   | Symbol           | Condition                  | Min.                 | Тур.        | Max.            | Unit     |  |

| V5 to V1 pins          |                  | Each cell voltage =        |                      |             |                 |          |  |

| Open-wire detection    | IVCL             | 3.6V                       | 30                   | 100         | 300             | nA       |  |

| sink current           |                  | Ta=0 to 60°C               |                      |             |                 |          |  |

| /ALARM pin             | Іона             | Ι <sub>ΟΗ</sub> =-100μΑ    | V <sub>DD</sub> -0.2 |             | V <sub>DD</sub> | V        |  |

| "H" output voltage     | ЮНА              | 10H=-100mA                 | VDD-0.2              |             | • 00            | v        |  |

| /ALARM pin             | Vola             | Vola lol=100µA             |                      |             | 0.2             | V        |  |

| "L" output voltage     | VOLA             | 10L=100μΑ                  | 0                    |             | 0.2             | v        |  |

| /ALARM pin             | Iolka            | Output state is Hi-Z       | -2                   |             | 2               | μA       |  |

| Output leakage current | IOLKA            |                            | -2                   |             | 2               | μΛ       |  |

| V5 to V2 pins          |                  | Internal balance FET       |                      |             |                 |          |  |

| Cell balance           | R <sub>BL1</sub> | Vn+1 – Vn = 0.3V           | 3                    | 6           | 12              | 0        |  |

| Switch ON resistance   | INBL1            | $V_{DD} - V2 \ge 6V$       | 5                    | 0           | 12              | 12       |  |

| Switch ON resistance   |                  | V <sub>DD</sub> =9V to 25V |                      |             |                 |          |  |

| V1 pin                 |                  | Internal balance FET       |                      |             |                 |          |  |

| Cell balance           | R <sub>BL2</sub> | V1=2.1V                    | 38                   | 57          | 91              | Ω        |  |

| Switch ON resistance   |                  | V <sub>DD</sub> =9V to 25V |                      |             |                 |          |  |

# • Supply Current Characteristics

|                     |        | 51151105               |                                                     |      |      |      |  |  |  |

|---------------------|--------|------------------------|-----------------------------------------------------|------|------|------|--|--|--|

|                     |        |                        | V <sub>DD</sub> =5 to 25V, GND=0 V, Ta=-20 to +85°C |      |      |      |  |  |  |

| Item                | Symbol | Condition              | Min.                                                | Тур. | Max. | Unit |  |  |  |

|                     |        | Each cell voltage=3.6V |                                                     |      |      |      |  |  |  |

|                     | IDD    | No output load         | —                                                   | 1    | 2    | μA   |  |  |  |

| Current consumption |        | Ta=0 to 60°C           |                                                     |      |      |      |  |  |  |

| Current consumption |        | Each cell voltage=3.6V |                                                     |      |      |      |  |  |  |

|                     | Iddt   | No output load         | —                                                   | 1    | 3    | μA   |  |  |  |

|                     |        | Ta=-20 to 85°C         |                                                     |      |      |      |  |  |  |

(Note) VDD pin current consumption. V5 to V1 pin input current, /ALARM pin output current is not included.

|                                                                   |                 | • • • •                                 |                       | V <sub>DD</sub> =18V, G | GND=0 V, Ta=0         | to 60°C |

|-------------------------------------------------------------------|-----------------|-----------------------------------------|-----------------------|-------------------------|-----------------------|---------|

| Item                                                              | Symbol          | Condition                               | Min.                  | Тур.                    | Max.                  | Unit    |

| Overvoltage detection<br>threshold                                | Vov             | Vov — Vov -25m                          |                       | Vov                     | V <sub>OV</sub> +25mV | V       |

| Overvoltage release                                               | Vovr            | Vov-Vovr≦50mV                           | Vovr -25m             | Vovr                    | Vovr +25m             | V       |

| threshold                                                         | VOVR            | $V_{OV}-V_{OVR}>50mV$                   | V <sub>OVR</sub> -35m | V <sub>OVR</sub>        | V <sub>OVR</sub> +35m | V       |

| Cell balancing detection<br>threshold                             | V <sub>CB</sub> | _                                       | V <sub>св</sub> -25mV | Vсв                     | V <sub>CB</sub> +25mV | V       |

| Cell balancing release                                            | Vcbr            | V <sub>CB</sub> -V <sub>CBR</sub> ≦50mV | V <sub>CBR</sub> -25m | VCBR                    | V <sub>CBR</sub> +25m | V       |

| threshold                                                         | V CBR           | $V_{B}-V_{CBR}>50mV$                    | V <sub>CBR</sub> -35m | V <sub>CBR</sub>        | V <sub>CBR</sub> +25m | V       |

| Open-wire detection /<br>release threshold                        | Vow             | _                                       | 0.5                   | 0.6                     | 0.7                   | V       |

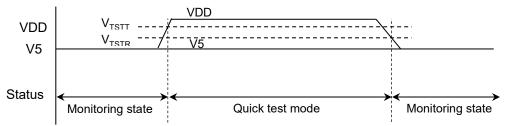

| Quick test mode<br>transition<br>VDD-V5 pin voltage<br>difference | Vtstt           | Ta=25°C                                 | 10                    | _                       | _                     | V       |

| Quick test mode<br>release<br>VDD-V5 pin voltage<br>difference    | Vtstr           | Ta=25°C                                 | 0                     | _                       | 3                     | V       |

#### • Detection Threshold Chracteristics (Ta=0 to 60°C)

# • Detection delay time characteristtics (Ta=0 to 60°C)

|                                                                                                                                                    | ine charac       |                                 | 00 C) | V <sub>DD</sub> =18V, GN | ND=0 V, Ta=0 | ) to 60°C |

|----------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------|-------|--------------------------|--------------|-----------|

| Item                                                                                                                                               | Symbol           | Condition                       | Min.  | Тур.                     | Max.         | Unit      |

| Cell voltage monitoring cycle                                                                                                                      |                  |                                 | 300   | 400                      | 500          | ms        |

| Cell voltage monitoring<br>term                                                                                                                    | t <sub>MON</sub> | —                               | 37    | 50                       | 63           | ms        |

| Cell balancing term                                                                                                                                | TBAL             |                                 | 262   | 350                      | 438          | ms        |

| Overvoltage detection<br>delay time setting range                                                                                                  | tov              | Defined with<br>detection cycle | 0     | _                        | 14           | cycle     |

| Cell balancing detection delay time setting range                                                                                                  | tсв              | Defined with<br>detection cycle | 0     | —                        | 14           | cycle     |

| Open-wire<br>detection/release delay<br>time setting range                                                                                         | tow              | Defined with detection cycle    | 0     | _                        | 14           | cycle     |

| Quick test mode<br>Cell voltage monitoring<br>cycle                                                                                                | <b>t</b> dett    | Ta=25°C                         | 75    | 100                      | 125          | ms        |

| Quick test mode<br>Cell balancing term                                                                                                             | <b>t</b> BALT    | Ta=25°C                         | 37    | 50                       | 63           | ms        |

| Quick test mode<br>Overvoltage detection<br>delay time,<br>Cell balancing detection<br>delay time,<br>open-wire<br>detection/release delay<br>time | tdlyt            | Defined with<br>detection cycle | _     | _                        | 1            | cycle     |

# • Code-001: Setting Parameters

V<sub>DD</sub>=18V, GND=0 V, Ta=0 to 60°C

| Item                                         | Symbol          | Condition                       | Min.  | Тур.  | Max.  | Unit  |

|----------------------------------------------|-----------------|---------------------------------|-------|-------|-------|-------|

| Overvoltage detection<br>threshold           | Vov             | _                               | 4.275 | 4.300 | 4.325 | V     |

| Overvoltage release<br>threshold             | Vovr            | _                               | 4.165 | 4.200 | 4.235 | V     |

| Cell balancing detection<br>threshold        | V <sub>CB</sub> | _                               | 4.075 | 4.100 | 4.125 | V     |

| Cell balancing release<br>threshold          | Vcbr            | _                               | 4.075 | 4.100 | 4.125 | V     |

| Overvoltage detection<br>delay time          | tov             | Defined with<br>detection cycle | 3     | _     | 4     | cycle |

| Cell balancing detection<br>delay time       | tсв             | Defined with<br>detection cycle | 1     | _     | 2     | cycle |

| Open-wire<br>detection/release delay<br>time | tow             | Defined with detection cycle    | 1     |       | 2     | cycle |

#### Functional Description

- Selecting the number of battery cells

- Number of battery cells is determined by part number. 5-cells=ML5206-001, 4-cells=ML5206-001A, 3-cells=ML5206-001B

#### /ALARM output pin

/ALARM pin output status for overvoltage/open-wire detected state.

|                                      | /ALARM pin output status |                               |                       |  |  |  |  |  |  |

|--------------------------------------|--------------------------|-------------------------------|-----------------------|--|--|--|--|--|--|

|                                      | CMOS                     | Nch open drain<br>(Code 001)  | Pch open drain        |  |  |  |  |  |  |

| Overvoltage/open-wire detected state | "L" level                | "L" level                     | "H" level             |  |  |  |  |  |  |

| Undetected state                     | "H" level                | "Hi-Z" level                  | "Hi-Z" level          |  |  |  |  |  |  |

| (mate d) (ALADNA mim and             | A shakes fam daha sha    | مامية مقمام منبيا مبير مقمقها | Ante any les versened |  |  |  |  |  |  |

(note 1) /ALARM pin output status for detected state and undetected state can be reversed.

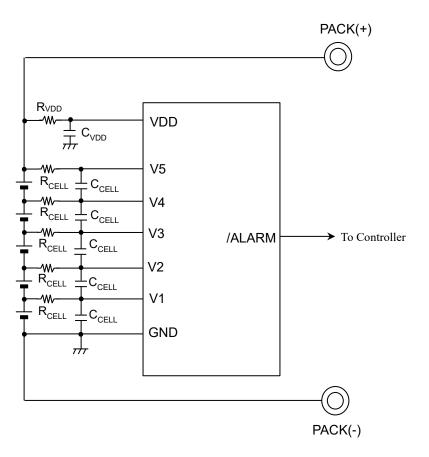

#### Handling VDD pin and V1 to V5 pins

Since the VDD pin is the power supply input, put a noise elimination RC filter in front of the VDD input for stabilization. The resistor value of this noise filter should be adjusted so that the voltage drop across the resistor is smaller than 0.3 V.

The V1 to V5 pins are the monitor pins for individual cell voltages. Put a noise elimination RC filter in front of each battery cell to prevent false detection.

#### Unused pin Treatment

The following table shows how to handle unused pins

| Unused pins | Recommended treatment |

|-------------|-----------------------|

| V1 , V2     | Connected to GND pin  |

#### Power-on/Power-off sequence

Battery cells can be connected in any order, but it is recommend that the lowest voltage cell is connected first, and then connection continues from lower to higher voltage cells, and the highest voltage cell is connected last. There are no restrictions on the power supply voltage rise time at power-on, and power-off sequence or power supply voltage fall time at power-off.

It may transition to the open-wire or overvoltage detection state if it takes long time to connect all cells.

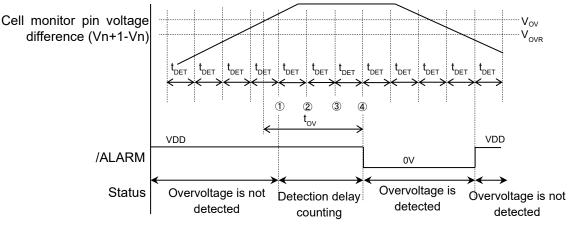

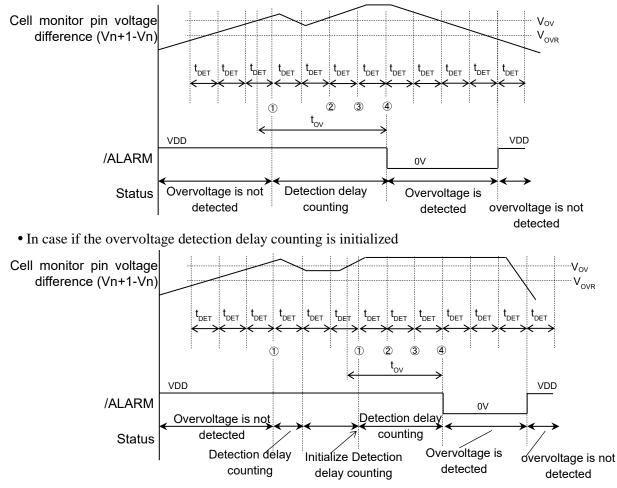

# Overvoltage detection function (In case if the overvoltage detection delay time = 3 detection cycles)

After power-on, cell voltage monitoring is started with cell voltage monitoring cycle of  $t_{DET}$  =400ms(typ). When any one or more battery cell voltages reach or exceed the overvoltage detection threshold Vov for series four times, it detects overvoltage state. And if /ALARM pin output type is CMOS output, /ALARM pin output changes from "H" level to "L" level.

If the state in which cell voltage of all cell is lower than overvoltage detection threshold  $V_{OV}$  is detected once, detection delay time is not initialized. But if it is detected for series two times, detection delay time counting is initialized.

After the overvoltage detection, if the cell voltage of all cell is lower than overvoltage release threshold  $V_{OVR}$ , and if /ALARM pin output type is CMOS output, /ALARM pin output changes from "L" level to "H" level.

• In case if the overvoltage detection delay counting is not initialized

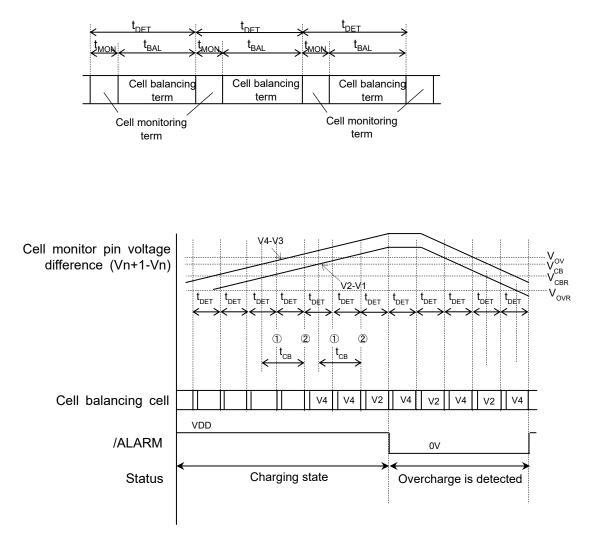

Cell balancing function (In case if the cell balancing detection delay time = 1 detection cycle)

After power-on, cell voltage monitoring is started with cell voltage monitoring cycle of  $t_{DET}$ =400ms(typ). When a cell voltage reach or exceed the cell balancing detection threshold V<sub>CB</sub> for series two times, the cell balancing switch of the cell is turned on. Not more than one cell balancing switches are turned on in the same time, but only one cell balancing switche is turned on in the order of V1 to V5.

When a cell voltage of the cell reach or below the cell balancing detection threshold  $V_{CB}$  for one time, the detection delay time counting is initialized.

For monitoring the cell voltage, in the cell monitoring term  $t_{MON}=50ms(typ)$ , cell balancing switch is automatically turned-off. The cell balancing switch is turned on during the call balancing term  $t_{BAL}=350ms(typ)$ .

If the cell voltage of which cell balancing switch is turned-on is decrease below cell balance release voltage  $V_{CBR}$ , cell balancing switch is turned off.

This cell balancing is operated independently each other.

If the connected cells is less then five, the cell balancing term is as much as the connected cells.

Cell balancing operation is shown below.

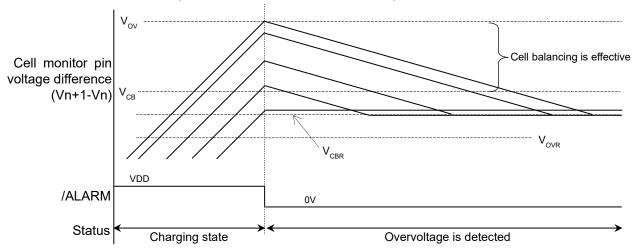

• In case if the cell balancing release threshold  $V_{CBR}$  > overvoltage release threshold  $V_{OVR}$

Cell balancing is executed at cells whose voltage is between over voltage detection threshold  $V_{\rm OV}$  and cell balancing detection threshold  $V_{\rm CB}$ .

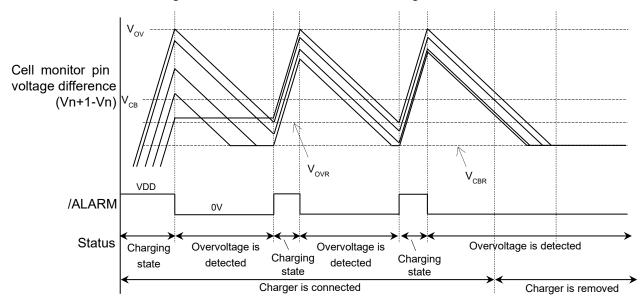

• In case if the overvoltage release threshold  $V_{OVR}$  > cell balancing release threshold  $V_{CBR}$

When the charger is connected, charging and discharging by cell balancing is repeated. When the charger is removed, the cell monitor voltage difference (Vn+1-Vn) will settle in cell balancing release threshold  $V_{CBR}$ .

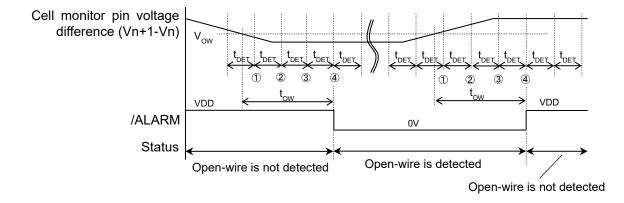

# Open-wire detection function (In case if the open-wire detection delay time = 3 detection cycles)

After power-on, cell voltage monitoring is started with cell voltage monitoring cycle of  $t_{DET}$ =400ms(typ). When any one or more battery cell voltages reach or below the open-wire detection threshold V<sub>OW</sub> for series four times. It detects open-weire state. And if /ALARM output type is CMOS output, /ALARM pin output changes from "H" level to "L" level.

If the state in which voltage of all cell is higher than open-wire detection threshold  $V_{OW}$  is detected for once, detection delay time counting is initialized.

After the open-wire detection, if the state in which cell voltage of all cell is higher than open-wire detection threshold  $V_{OW}$  is detected for series four times, and if /ALARM output type is CMOS output, /ALARM pin output changes from "L" level to "H" level.

If the state in which cell voltage of one or more cell is lower than open-wire detection threshold  $V_{OW}$  is detected for once, detection delay time counting is initialized.

#### Quick test mode

In the Quick test mode, cell voltage monitoring cycle is 100ms(typ), cell balancing term is 50ms(typ), overvoltage/cell balancing detection delay time and open-wire detection/release delay time are set shorter than one detection cycle.

If the voltage of VDD pin is more than 10V higher than V5 pin, the state changes into this quick test mode.

For recovering from quick test mode to normal mode, set the difference voltage of V5 and VDD pin lower than 3V".

This test mode can decrease the test time after board mounting.

#### Redefinition of overvoltage / release voltage, cell balancing detection / release voltage Setting Range and Step

The threshold for Overvoltage detection, Overvoltage Release voltage, Cell Balancing Threshold, and Cell Balancing Release voltage are ROM code selectable per this table. Since some combinations are unavailable, contact us for details.

| Detection voltage                                     | Setting range                 | Step voltage |

|-------------------------------------------------------|-------------------------------|--------------|

| Overvoltage detection<br>threshold V <sub>OV</sub>    | 4.0V to 4.4V                  | 5mV          |

| Overvoltage release threshold<br>V <sub>OVR</sub>     | V <sub>OV</sub> -(0 to 200mV) | 10mV         |

| Cell balancing detection<br>threshold V <sub>CB</sub> | 4.0V to 4.4V                  | 5mV          |

| Cell balancing release<br>threshold V <sub>CBR</sub>  | V <sub>CB</sub> -(0 to 200mV) | 10mV         |

#### Redefinition of overvoltage / cell balancing Detection Delay time and open-wire Detection/Relase Delay Time Range

The overvoltage detection delay time and open-wire detection/release delay time are ROM code selectable per these tables.

| Delay time      |    | Settable time (detection cycle) |    |    |    |    |    |    |    |    |    |    |    |    | Unit  |

|-----------------|----|---------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|-------|

| Overvoltage     | 0  | 1                               | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 12 | 13 | 14 |       |

| detection delay | to | to                              | to | to | Т0 | to | cycle |

| time            | 1  | 2                               | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 13 | 14 | 15 |       |

| cell balancing  | 0  | 1                               | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 12 | 13 | 14 |       |

| detection delay | to | to                              | to | to | Т0 | to | cycle |

| time            | 1  | 2                               | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 13 | 14 | 15 |       |

| Open-wire       | 0  | 1                               | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 12 | 13 | 14 |       |

| detection/relea | to | to                              | to | to | Т0 | to | cycle |

| se delay time   | 1  | 2                               | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 13 | 14 | 15 |       |

| Delay time      |     | Settable time (monitoring cycle=400ms) |     |     |     |     |     |     |     |     |     |     |     |     | Unit |

|-----------------|-----|----------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|------|

| Overvoltage     | 0   | 0.4                                    | 0.8 | 1.2 | 1.6 | 2.0 | 2.4 | 2.8 | 3.2 | 3.6 | 4.0 | 4.4 | 4.8 | 5.2 |      |

| detection delay | to  | to                                     | to  | to  | to  | to  | to  | to  | to  | to  | to  | to  | to  | to  | sec  |

| time            | 0.4 | 0.8                                    | 1.2 | 1.6 | 2.0 | 2.4 | 2.8 | 3.0 | 3.6 | 4.0 | 4.4 | 4.8 | 5.2 | 5.6 |      |

| cell balancing  | 0   | 0.4                                    | 0.8 | 1.2 | 1.6 | 2.0 | 2.4 | 2.8 | 3.2 | 3.6 | 4.0 | 4.4 | 4.8 | 5.2 |      |

| detection delay | to  | to                                     | to  | to  | to  | to  | to  | to  | to  | to  | to  | to  | to  | to  | sec  |

| time            | 0.4 | 0.8                                    | 1.2 | 1.6 | 2.0 | 2.4 | 2.8 | 3.0 | 3.6 | 4.0 | 4.4 | 4.8 | 5.2 | 5.6 |      |

| Open-wire       | 0   | 0.4                                    | 0.8 | 1.2 | 1.6 | 2.0 | 2.4 | 2.8 | 3.2 | 3.6 | 4.0 | 4.4 | 4.8 | 5.2 |      |

| detection/relea | to  | to                                     | to  | to  | to  | to  | to  | to  | to  | to  | to  | to  | to  | to  | sec  |

| se delay time   | 0.4 | 0.8                                    | 1.2 | 1.6 | 2.0 | 2.4 | 2.8 | 3.0 | 3.6 | 4.0 | 4.4 | 4.8 | 5.2 | 5.6 |      |

### Application Circuit Example (5-cell system)

Recommended values for External Components

| Component        | Recommended<br>Value |  |

|------------------|----------------------|--|

| R <sub>VDD</sub> | 1kΩ                  |  |

| CVDD             | 4.7μF                |  |

| Rcell            | 51 Ω                 |  |

| CCELL            | 0.1µF                |  |

#### Package Dimensions

#### Caution regarding surface mount type packages

Surface mount type packages are susceptible to heat applied in solder reflow and moisture absorbed during storage. Please contact your local ROHM sales representative for recommended mounting conditions (reflow sequence, temperature and cycles) and storage environment.

# Revision History

|              |              | Page    |          |                             |

|--------------|--------------|---------|----------|-----------------------------|

| Document No. | Issue date   | Before  | After    | Revision Description        |

|              |              | rvision | revision |                             |

| FEDL5206-01  | 2020.11.27   | _       | _        | First edition               |

| FEDL5206-02  | Jan. 9, 2024 | 1       | 1        | Add Application Part number |

|              |              | 16      | 16       | Add Notes                   |

Notes

- When using LAPIS Technology Products, refer to the latest product information and ensure that usage conditions (absolute maximum ratings<sup>\*1</sup>, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures.

\*1: Absolute maximum ratings: a limit value that must not be exceeded even momentarily.

- 2) The Products specified in this document are not designed to be radiation tolerant.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore, LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) LAPIS Technology intends our Products to be used in a way indicated in this document. Please be sure to contact a ROHM sales office if you consider the use of our Products in different way from original use indicated in this document. For use of our Products in medical systems, please be sure to contact a LAPIS Technology representative and must obtain written agreement. Do not use our Products in applications which may directly cause injuries to human life, and which require extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us without our prior written consent.

- 6) All information contained in this document is subject to change for the purpose of improvement, etc. without any prior notice. Before purchasing or using LAPIS Technology Products, please confirm the latest information with a ROHM sales office. LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document, however, LAPIS Technology shall have no responsibility for any damages, expenses or losses arising from inaccuracy or errors of such information.

- 7) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 8) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 9) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 10) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

(Note) "LAPIS Technology" as used in this document means LAPIS Technology Co., Ltd.

Copyright 2020 – 2024 LAPIS Technology Co., Ltd.

# LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan https://www.lapis-tech.com/en/