#### Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

# RB-S22Q53xTB48 User's Manual

Issue Date: February 5, 2021

#### Notes

- 1) The information contained herein is subject to change without notice.

- 2) When using LAPIS Technology Products, refer to the latest product information (data sheets, user's manuals, application notes, etc.), and ensure that usage conditions (absolute maximum ratings, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. You are responsible for evaluating the safety of the final products or systems manufactured by you.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (AV/OA devices, communication, consumer systems, gaming/entertainment sets, etc.) as well as the applications indicated in this document. For use of our Products in applications requiring a high degree of reliability (as exemplified below), please be sure to contact a LAPIS Technology representative and must obtain written agreement: transportation equipment (cars, ships, trains, etc.), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us. Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Technology does not warrant that such information is error-free and LAPIS Technology shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 8) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 9) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act..

- 10) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 11) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

(Note) "LAPIS Technology" as used in this document means LAPIS Technology Co., Ltd.

Copyright 2019 – 2021 LAPIS Technology Co., Ltd.

### LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan https://www.lapis-tech.com/en/

### **Table of Contents**

| 1. | Ove  | rview                                   | 1 |

|----|------|-----------------------------------------|---|

| 2. | Оре  | rviewrational notes                     | 1 |

| 3. | Spe  | cification                              | 2 |

| 3  | .1.  | VDDR jumper pin                         |   |

| 3  | .2.  | IRON jumper pin                         |   |

| 3  | .3.  | LOUT jack                               |   |

| 3  | .4.  | SP jack                                 |   |

| 3  | .5.  | AIN through hall                        |   |

| 3  | .6.  | SPVDD jumper terminal, EXT through hall |   |

| 3  | .7.  | SAD2-0 lands                            |   |

| 3  | .8.  | XT1 land, J1 land                       |   |

| 3  | .9.  | Connection of FB1,FB2 pin               |   |

| 3  | .10. | CN1 connector                           |   |

| 3  | .11. | CN2 connector                           | 5 |

| 3  | .12. | CN3 connector                           |   |

| 4. | App  | endix                                   | 7 |

| 4  | .1.  | PCB layout                              | 7 |

| 4  | .2.  | BOM list, Schematic                     |   |

| 5. | Rev  | ision History                           |   |

|    |      |                                         |   |

#### 1. Overview

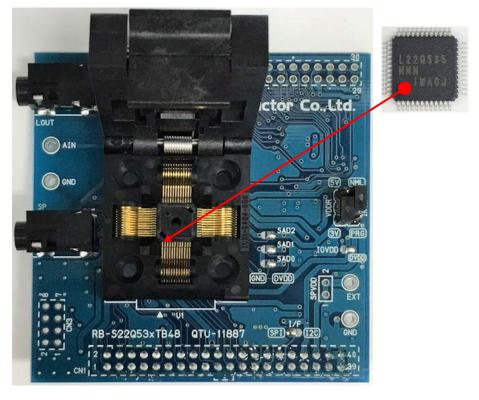

This instruction manual is for the RB-S22Q53xTB48 which is the reference board for ML22Q532/ML22Q533/ML22Q535 (hereinafter referred to as "Speech Synthesis LSIs").

This board can be combined with Sound Device Control Board 3 (hereinafter referred to as "SDCB3") to do the following:

- Voice playback by ML22Q532/ML22Q533/ML22Q535.

- Writing sound code data into ML22Q532/ML22Q533/ML22Q535.

#### 2. Operational notes

The following describes the precautions to follow when handling the RB-S22Q53xTB48.

- Turn off the power when attaching the RB-S22Q53xTB48 to the SDCB3.

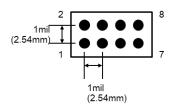

- Turn off the power when loading Speech Synthesis LSIs into the RB-S22Q53xTB48. Pin 1 is the position of the board silk ▲ at the bottom left with respect to the socket opening. The Figure 1 shows the setting directions of Speech Synthesis LSIs.

- The ML22Q532/ML22Q533/ML22Q535 supply voltages are 2.7 to 3.6V / 3.3 to 5.5V. Use the RB-S22Q53xTB48 with a power supply voltage of 3.0V.

- Connect LOUT jack and SP jack to the mono speaker.

- This board cannot use the playback sound error detection function targeting FB1,FB2 pin inputs of Speech Synthesis LSIs. (Refer to 3.9. Connection of FB1,FB2 pin)

- RB-S22Q53xTB48 is a device used only by experts in R&D facilities for research and development purposes. RB-S22Q53xTB48 is not intended to be used in mass-produced products or parts thereof.

- The information in this document is subject to change without notice due to product improvement and technological improvement. Prior to use, please ensure that the information is up to date.

- LAPIS Technology does not provide any RB-S22Q53xTB48 support. Replace only in case of initial failure.

Figure 1 Outline Diagram

#### 3. Specification

#### 3.1. VDDR jumper pin

VDDR jumper pin is jumper pin that switch the connection of VDDR pin of Speech Synthesis LSIs.

| VDDR | Contents                       |  |  |  |  |

|------|--------------------------------|--|--|--|--|

| 3V   | VDDR pin is connected to DVDD. |  |  |  |  |

| 5V   | VDDR pin is open.              |  |  |  |  |

Set to 3V when connecting to a SDCB3 for use.

#### 3.2. IRON jumper pin

IRON jumper pin is jumper pin that switch the connection of IRON pin of Speech Synthesis LSIs.

| IRON | Contents                          |

|------|-----------------------------------|

| NML  | IRON pin is connected to CN1,CN2. |

| PRG  | IRON pin is connected to IOVDD.   |

Set to NML when connecting to SDCB3 for use. IRON pin is controlled from SDCB3. When this board is used by itself, setting PRG enables the flash memory interface of Speech Synthesis LSIs.

#### 3.3. LOUT jack

LOUT jack is a jack where the signal from LOUT pins of Speech Synthesis LSIs is output via the speaker amplifier. Set Mode of Play setting of SDCB Controller to Line AMP(LOUT). (Refer to Speech LSI Utility User's Manual.) Connect a monaural speaker.

#### 3.4. SP jack

SP jack is a jack where the signal from SPP,SPM pins of Speech Synthesis LSIs is output. Set Mode of Play setting of SDCB Controller to Speaker AMP. (Refer to Speech LSI Utility User's Manual.) Connect a monaural speaker.

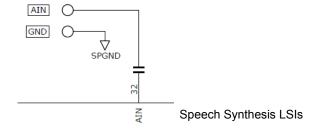

#### 3.5. AIN through hall

AIN through hole is used to input signals from an external source to the AIN pin of Speech Synthesis LSIs. Input the speaker amplifier input signal to AIN through hole.

Figure 2 AIN through hall

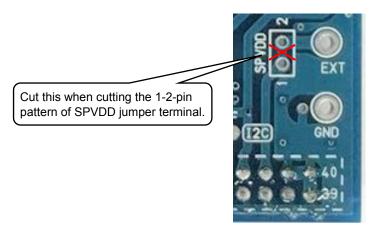

#### 3.6. SPVDD jumper terminal, EXT through hall

SPVDD jumper terminal is used to switch the destination of SPVDD pins of Speech Synthesis LSIs.

When supplying from SDCB3, connect 1-2pin of SPVDD jumper terminal.

To supply from an external source, cut the pattern between 1 and 2 pins of SPVDD jumper terminal and input SPVDD from the EXT throughhole.

Figure 3 SPVDD jumper terminal

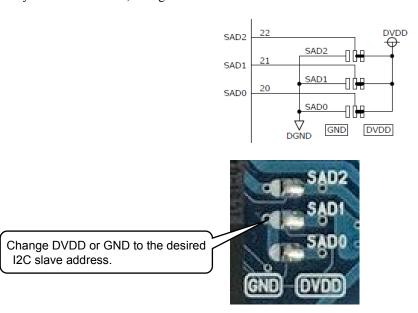

#### 3.7. SAD2-0 lands

SAD2-0 lands are used to change SAD2-0 setting of Speech Synthesis LSIs.

This board is shipped to DVDD (I2C slave address is 111 101).

When connecting this board to SDCB3 and using it, set DVDD to the factory default settings.

To set any I2C slave address, change the connection of SAD2-0 lands.

Figure 4 SAD2-0 lands

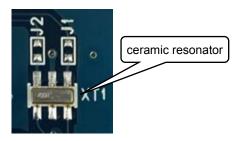

#### 3.8. XT1 land, J1 land

XT1 land is used to mount the Ceramic resonator.

When using a ceramic resonator for the clock of Speech Synthesis LSIs, mount the components.

When no component is mounted, Speech Synthesis LSIs operates with built-in RC oscillation.

Figure 5 Ceramic resonator

A typical example of a ceramic resonator that matches XT1 land foot pattern is shown below.

| Vendor                         | Frequency[Hz] | Parts Number     |

|--------------------------------|---------------|------------------|

| Murata Manufacturing Co., Ltd. | 4M            | CSTCR4M00G55B-R0 |

| Murata Manufacturing Co., Ltd. | 4.096M        | CSTCR4M09G55B-R0 |

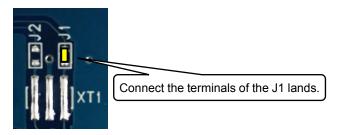

J1 land is land connecting the XT pin of speech synthesis LSIs to the 28pin (XT) of CN2.

To use an external clock for Speech Synthesis LSIs clock, connect the pins of the J1 land and input them from the 28pin (XT) of CN2.

Figure 6 J1 land

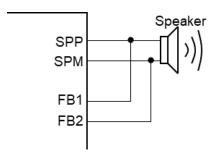

#### 3.9. Connection of FB1,FB2 pin

This board cannot use the playback sound error detection function targeting FB1,FB2 pin inputs of Speech Synthesis LSIs. However, LSI internal playback sound error detection function can be used.

#### CAUTION: This board is incorrect.

When using the playback sound error detection function targeting FB1,FB2 pin, connect the signal output from the SPP pin to FB1 pin and the signal output from the SPM pin to FB2 pin on the customer's board.

Figure 7 Connection example of FB1, FB2 pins and the SPP, SPM pins

#### 3.10. CN1 connector

CN1 connector is used to connect to SDCB3.

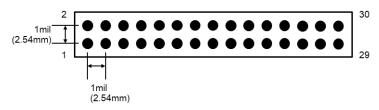

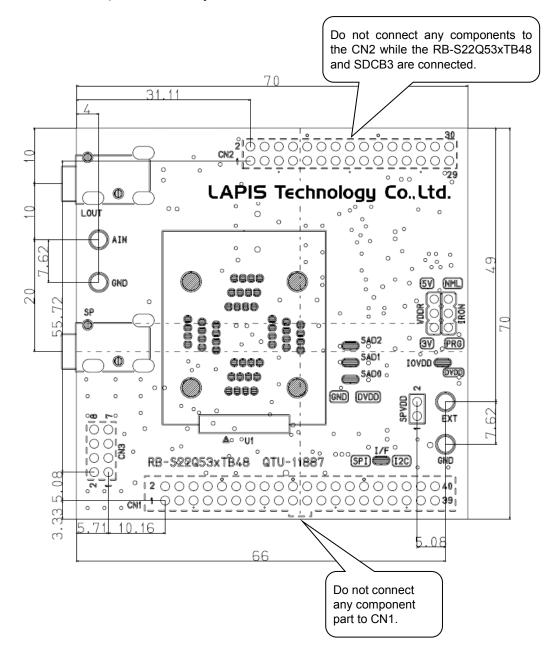

#### 3.11. CN2 connector

CN2 connector is used to connect to the pins of Speech Synthesis LSIs.

| CN2           | LSI    |          | I/O                |             |  |

|---------------|--------|----------|--------------------|-------------|--|

| Pin No        | Pin No | Pin Name | SDCB3 connection   | Single unit |  |

| 1             | 26     | DVDD *1  | 0                  | I           |  |

| 2             | 26     | DVDD*1   | 0                  | I           |  |

| 3             | 43     | RESETB   | 0                  | I           |  |

| 4             | 44     | TEST0    | 0                  | I           |  |

| 5             | 45     | STATUS1  | 0                  | 0           |  |

| 6             | 46     | STATUS2  | 0                  | 0           |  |

| 7             | 47     | CBUSYB   | 0                  | 0           |  |

| 8             | -      | -        | -                  | -           |  |

| 9             | 2      | SCL      | 0                  | I           |  |

| 10            | 3      | SDA      | 0                  | I/O         |  |

| 11            | 8      | CSB      | 0                  | I           |  |

| 12            | 9      | SCK      | 0                  | 1           |  |

| 13            | 10     | SI       | 0                  | I           |  |

| 14            | 11     | SO       | 0                  | 0           |  |

| 15            | 1, 25  | DGND     | -                  | -           |  |

| 16            | 1, 25  | DGND     | 1                  | -           |  |

| 17            | 13     | IRCSB    | 0                  | 1           |  |

| 18            | 14     | IRSCK    | 0                  | 1           |  |

| 19            | 15     | IRSO     | 0                  | 0           |  |

| 20            | 16     | IRSI     | 0                  | I           |  |

| 21            | 17     | IRON     | 0                  | I           |  |

| 22            | -      | -        | -                  | -           |  |

| 23            | 18     | IOVDD*1  | 0                  | 0           |  |

| 24            | 19     | VDDR     | 0                  | 0           |  |

| 25            | 1, 25  | DGND     | -                  | -           |  |

| 26            | 1, 25  | DGND     | -                  | -           |  |

| 27            | 23     | XTB *2   | 0                  | 0           |  |

| 28            | 24     | XT *2    | 0                  | 1           |  |

| 29            | 1, 25  | DGND     | -                  | -           |  |

| 30 1, 25 DGND |        | -        | -<br>nacting CDCD2 |             |  |

<sup>\*1</sup> Do not supply DVDD,IOVDD from CN2 when connecting SDCB3.

<sup>\*2</sup> When the J1 and J2 lands are connected, the XT and XTB pins of Speech Synthesis LSIs are input and output.

Figure 8 CN2 connectors hole pattern

#### 3.12. CN3 connector

CN3 connector is used to connect to the serial audio interface pin of Speech Synthesis LSIs.

| CNI2          | LSI        |          | I/O              |             |  |

|---------------|------------|----------|------------------|-------------|--|

| CN3<br>Pin No | Pin No     | Pin Name | SDCB3 connection | Single unit |  |

| 1             | 26         | DVDD*    | 0                | 1           |  |

| 2             | 26         | DVDD*    | 0                | I           |  |

| 3             | 4          | LRCLK    | I                | 1           |  |

| 4             | 5          | BCLK     | I                | 1           |  |

| 5             | 6 SAI_IN   |          | I                | 1           |  |

| 6 7 SAI_OL    |            | SAI_OUT  | 0                | 0           |  |

| 7             | 1, 25      | DGND     | -                | -           |  |

| 8             | 1, 25 DGND |          | -                | -           |  |

Figure 9 CN3 connectors hole pattern

### 4. Appendix

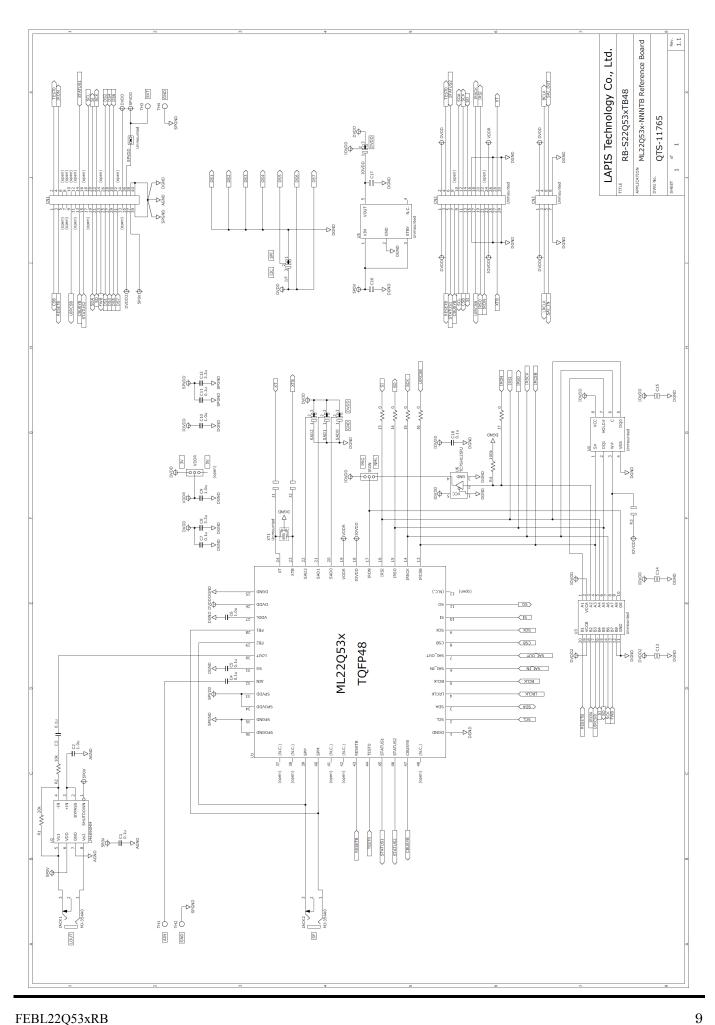

#### 4.1. PCB layout

Figure 10 shows the RB-S22Q53xTB48 PCB layout.

Figure 10 PCB layout

# LAPIS Technology Co., Ltd.

### 4.2. BOM list, Schematic

|    | Parts Number            | Symbol                  | Contents                           | Qty. | Vendor                           |

|----|-------------------------|-------------------------|------------------------------------|------|----------------------------------|

| 1  | QTU-11887               | RB-S22Q53xTB48          | PCB                                | 1    | LAPIS Technology Co., Ltd.       |

| 2  | CGA3E2X7R1E104K080AA    | C1,C3,C4,C5,<br>C7,C11  | Ceramic Capacitor<br>0.1µF/25V X7R | 6    | TDK Corporation                  |

| 3  | CGA3E1X7R1C105K080AC    | C2,C6,C9,C10,<br>C18    | Ceramic Capacitor<br>1.0µF/16V X7R | 5    | TDK Corporation                  |

| 4  | C1608X5R1C335K080AC     | C8,C12                  | Ceramic Capacitor<br>3.3µF/16V X5R | 2    | TDK Corporation                  |

| 5  | HIF3FB-40DA-2.54DSA(71) | CN1                     | 40pin Receptacle                   | 1    | Hirose Electric Co., Ltd.        |

| 6  | A2-3PA-2.54DSA          | IRON,VDDR               | 3pin Pin Header                    | 2    | Hirose Electric Co., Ltd.        |

| 7  | -                       | I/F,IOVDD               | Select pad                         | 2    | -                                |

| 8  | MCR03EZPJ000            | J3,J4,J5,J6,J7          | Resistor 0Ω                        | 5    | Rohm Co., Ltd.                   |

| 9  | MJ-354A0                | JACK1,JACK2             | 2-Conductor Miniature Jack         | 2    | MARUSHIN ELECTRIC MFG. CO., LTD. |

| 10 | MCR03EZPJ203            | R1                      | Resistor 20kΩ ±5%                  | 1    | Rohm Co., Ltd.                   |

| 11 | MCR03EZPJ103            | R2                      | Resistor 10kΩ ±5%                  | 1    | Rohm Co., Ltd.                   |

| 12 | MCR03EZPJ104            | R4                      | Resistor 100kΩ ±5%                 | 1    | Rohm Co., Ltd.                   |

| 13 | -                       | SAD0,SAD1,SAD2          | Select pad                         | 3    | -                                |

| 14 | IC51-806.A106725-001    | U1                      | TQFP P0.50<br>48P Socket           | 1    | YAMAICHI ELECTRONICS Co., Ltd.   |

| 15 | LM4890MM/NOPB           | U2                      | Audio Power Amplifier              | 1    | Texas Instruments Incorporated   |

| 16 | TC7SH125FU              | U6                      | Bus Buffer with 3-State<br>Output  | 1    | Toshiba Corporation              |

| 17 | HIF3GA-2.54SP           | -                       | Short Pin                          | 2    | Hirose Electric Co., Ltd.        |

| 18 | -                       | C13,C14,C15,C16,<br>C17 | Unmounted                          | 5    | -                                |

| 19 | -                       | CN2                     | Unmounted                          | 1    | -                                |

| 20 | -                       | CN3                     | Unmounted                          | 1    | -                                |

| 21 | •                       | J1,J2                   | Unmounted                          | 2    | -                                |

| 22 | -                       | SPVDD                   | Unmounted                          | 1    | -                                |

| 23 | -                       | R3                      | Unmounted                          | 1    | -                                |

| 24 | -                       | TH1,TH2,TH3,TH4         | Unmounted                          | 4    | -                                |

| 25 | -                       | U3                      | Unmounted                          | 1    | -                                |

| 26 | -                       | U4                      | Unmounted                          | 1    | -                                |

| 27 | -                       | U5                      | Unmounted                          | 1    | -                                |

| 28 | -                       | XT1                     | Unmounted                          | 1    | -                                |

# LAPIS Technology Co., Ltd.

# LAPIS Technology Co., Ltd.

## 5. Revision History

|                 |                     | Page                |                |                                                                                                                                                   |

|-----------------|---------------------|---------------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| Document No.    | Issue Date          | Previous<br>Edition | New<br>Edition | Description                                                                                                                                       |

| FEBL22Q53xRB-01 | October 31,<br>2019 | -                   | -              | First edition.                                                                                                                                    |

| FEBL22Q53xRB-03 | March 26,<br>2020   | 3                   | 3              | 3.3. BOM list, Schematic                                                                                                                          |

| FEBL22Q53xRB-04 | February 5          | Notes               | Notes          | Change the description.                                                                                                                           |

|                 | 2021                |                     |                | Company name change.                                                                                                                              |

|                 |                     | 1                   | 1              | Operational notes     Added to connect a monaural speaker to the LOUT jack and SP jack.                                                           |

|                 |                     |                     |                | 2. Operational notes Added that playback sound error detection function for FB1,FB2 pins cannot be used.                                          |

|                 |                     | -                   | 2              | 3.1. VDDR jumper pin<br>Added chapter.                                                                                                            |

|                 |                     |                     |                | 3.2. IRON jumper pin<br>Added chapter.                                                                                                            |

|                 |                     |                     |                | 3.3. LOUT jack Changed chapter number. Added SDCB Controller settings when using LOUT jack. Added to connect a monaural speaker to the LOUT jack. |

|                 |                     |                     |                | 3.4. SP jack Changed chapter number. Added SDCB Controller settings when using SP jack. Added to connect a monaural speaker to the LOUT jack.     |

|                 |                     |                     |                | 3.5. AIN through hall Changed chapter number. Changed chapter name. Added connection diagram.                                                     |

|                 |                     | -                   | 3              | 3.6, SPVDD jumper terminal, EXT through hall Added chapter.                                                                                       |

|                 |                     |                     |                | 3.7, SAD2-0 lands<br>Added chapter.                                                                                                               |

|                 |                     |                     |                | 3.8. XT1 land, J1 land Changed chapter number. Changed chapter name. Added operation in RC oscillation.                                           |

|                 |                     | -                   | 4              | 3.9. Connection of FB1,FB2 pin Added chapter.                                                                                                     |

|                 |                     |                     |                | 3.10. CN1 connector<br>Changed chapter number.                                                                                                    |

|                 |                     | -                   | 5              | 3.11. CN2 connector<br>Changed chapter number.<br>Added input/output directions when SDCB3 is<br>connected and single unit is used.               |

| - | 6 | 3.12. CN3 connector Changed chapter number. Added input/output directions when SDCB3 is connected and single unit is used. |

|---|---|----------------------------------------------------------------------------------------------------------------------------|

| - | 7 | Appendix     Added chapter.                                                                                                |

|   |   | 4.1. PCB layout<br>Changed chapter number.<br>Changed Figure 10.                                                           |

| - | 8 | 4.2. BOM list, Schematic Changed chapter number. Company name change.                                                      |

| - | 9 | 4.2. BOM list, Schematic Changed chapter number. Company name change.                                                      |