Dear customer

LAPIS Semiconductor Co., Ltd. ("LAPIS Semiconductor"), on the 1<sup>st</sup> day of October, 2020, implemented the incorporation-type company split (shinsetsu-bunkatsu) in which LAPIS established a new company, LAPIS Technology Co., Ltd. ("LAPIS Technology") and LAPIS Technology succeeded LAPIS Semiconductor's LSI business.

Therefore, all references to "LAPIS Semiconductor Co., Ltd.", "LAPIS Semiconductor" and/or "LAPIS" in this document shall be replaced with "LAPIS Technology Co., Ltd."

Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

LAPIS Technology Co., Ltd.

October 1, 2020

# ML2272X Reference Board User's Manual

**NOTICE**

1. The information contained herein can change without notice owing to product and/or technical improvements. Before using

the product, please make sure that the information being referred to is up-to-date.

2. The outline of action and examples for application circuits described herein have been chosen as an explanation for the

standard action and performance of the product. When planning to use the product, please ensure that the external

conditions are reflected in the actual circuit, assembly, and program designs.

3. When designing your product, please use our product below the specified maximum ratings and within the specified

operating ranges including, but not limited to, operating voltage, power dissipation, and operating temperature.

4. LAPIS SEMICONDUCTOR CO., LTD. assumes no responsibility or liability whatsoever for any failure or unusual or

unexpected operation resulting from misuse, neglect, improper installation, repair, alteration or accident, improper handling,

or unusual physical or electrical stress including, but not limited to, exposure to parameters beyond the specified maximum

ratings or operation outside the specified operating range.

5. Neither indemnity against nor license of a third party's industrial and intellectual property right, etc. is granted by us in

connection with the use of the product and/or the information and drawings contained herein. No responsibility is assumed

by us for any infringement of a third party's right which may result from the use thereof.

6. The products listed in this document are intended for use in general electronics equipment for commercial applications (e.g.,

office automation, communication equipment, measurement equipment, consumer electronics, etc.). These products are not,

unless specifically authorized by LAPIS SEMICONDUCTOR CO., LTD., authorized for use in any system or application

that requires special or enhanced quality and reliability characteristics nor in any system or application where the failure of

such system or application may result in the loss or damage of property, or death or injury to humans.

Such applications include, but are not limited to, traffic and automotive equipment, safety devices, aerospace equipment,

nuclear power control, medical equipment, and life-support systems.

7. Certain products in this document may need government approval before they can be exported to particular countries. The

purchaser assumes the responsibility of determining the legality of export of these products and will take appropriate and

necessary steps at their own expense for these.

8. No part of the contents contained herein may be reprinted or reproduced without our prior permission.

Copyright 2011 LAPIS SEMICONDUCTOR CO., LTD.

1

## 1. Overview

This is the instruction manual for ML2272X Reference Board

ML2272X Reference Board supports following functions in combination with Sound Device Control Board.

- 1. Voice Playback by ML2272X

- 2. Writing voice data into ML2272X.

Please notice that the LSI written by this reference board can be used only as a prototype.

It is not guaranteed as a mass-produced quality.

# 2 . Operating Suggestions

It is the operating suggestions for ML2272X Reference Board.

- 1. Please do not supply a power to sound device control board, when the reference board is being mounted on it.

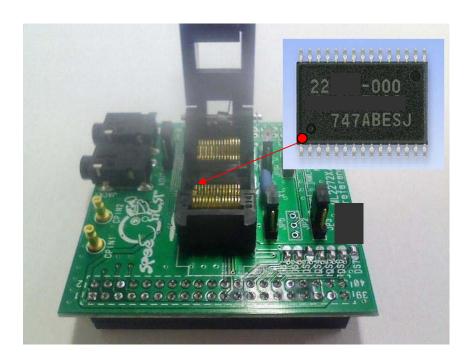

- 2. Please do not supply a power to sound device control board, when the LSIs are being mounted in the socket on the reference board. Then please confirm the aspect of the LSIs. The pin no.1 of LSIs must be placed at left near side of the socket.

- LAPIS SEMICONDUCTOR will not provide any support for this board, but the board can be exchanged with a new product only when it has an initial failure.

# 3 . Reference Board

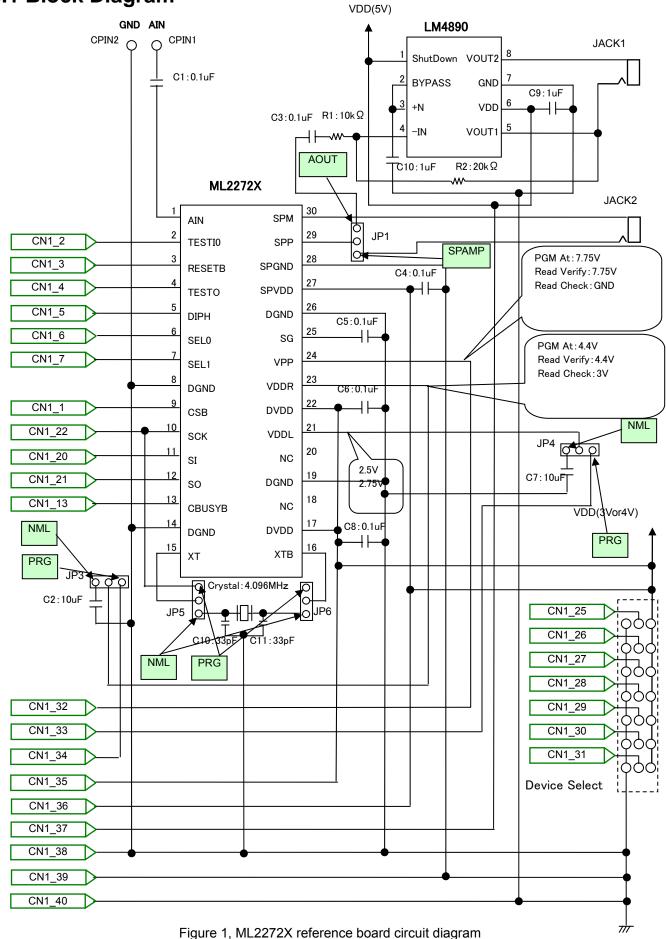

#### 3.1 Block Diagram

#### 3.2 Rough PCB layout

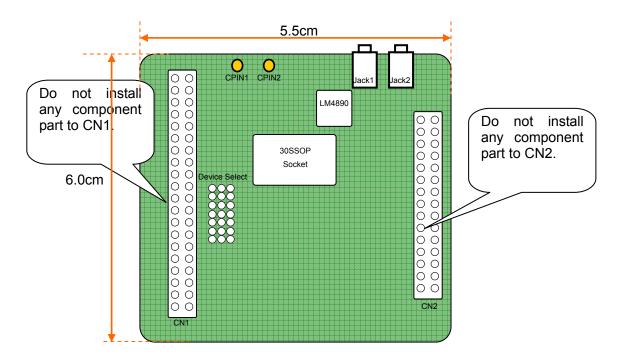

ML2272X reference board rough layout is described.

Figure 2, ML2272X reference board rough layout

## 3.3 CN1 connector pin connections

| CN1 | Pin No         | Connect LSI | LSI Pin No | LSI Pin Name    |

|-----|----------------|-------------|------------|-----------------|

| 1   | I/O            | ML2272X     | 9          | CSB             |

| 2   | I/O            | ML2272X     | 2          | TESTI0          |

| 3   | I/O            | ML2272X     | 3          | RESETB          |

| 4   | I/O            | ML2272X     | 4          | TESTO           |

| 5   | I/O            | ML2272X     | 5          | DIPH            |

| 6   | I/O            | ML2272X     | 6          | SEL0            |

| 7   | I/O            | ML2272X     | 7          | SEL1            |

| 8   | I/O            | _           | _          | _               |

| 9   | I/O            | _           | _          | _               |

| 10  | I/O            | _           | _          | _               |

| 11  | I/O            | _           | _          | _               |

| 12  | I/O            | _           | _          | _               |

| 13  | I/O            | ML2272X     | 13         | CBUSYB          |

| 14  | I/O            | _           | _          | _               |

| 15  | I/O            | _           | _          | _               |

| 16  | I/O            | _           | _          | _               |

| 17  | I/O            | _           | _          | _               |

| 18  | I/O            | _           | _          | _               |

| 19  | I/O            | _           | _          | _               |

| 20  | I/O            | ML2272X     | 11         | SI              |

| 21  | I/O            | ML2272X     | 12         | SO              |

| 22  | I/O            | ML2272X     | 10         | SCK             |

| 23  | I/O            | _           | _          | _               |

| 24  | I/O            | _           | _          | _               |

| 25  | Device Select  | GND         | _          | _               |

| 26  | Device Select  | GND         | _          | _               |

| 27  | Device Select  | VDD         | _          | _               |

| 28  | Device Select  | GND         | _          | _               |

| 29  | Device Select  | GND         | _          | _               |

| 30  | Device Select  | GND         | _          | _               |

| 31  | Device Select  | VDD         | _          | _               |

| 32  | VPP            | ML2272X     | 24         | TESTI1(VPP)     |

| 33  | VDD()          | JP4         | 1          | _               |

| 34  | VDD(3V)        | JP3         | 1          | _               |

| 35  | VDD (Variable) | ML2272X     | 17,22      | _               |

| 36  | VDD(3V)        | ML2272X     | 27         | SPVDD           |

| 37  | VDD(5V)        | LM4890      | 6<br>1     | VDD<br>ShutDown |

| 38  | GND            | ML2272X     | 8,14,19,26 | DGND            |

| 39  | GND            | ML2272X     | 28         | SPGND           |

| 40  | GND            | LM4890      | 7          | GND             |

### 3.4 CN2 connector specification

CN2 is connecting to all ML2272X terminals. It has two rows 30 pins.

Figure 3, CN2 connectors hole pattern

#### 3.5 CN2 connector pin connections

| CN2 Pin No | LSI Pin No | LSI Pin Name |

|------------|------------|--------------|

| 1          | 1          | AIN          |

| 2          | 2          | TESTI0       |

| 3          | 3          | RESETB       |

| 4          | 4          | TESTO        |

| 5          | 5          | DIPH         |

| 6          | 6          | SEL0         |

| 7          | 7          | SEL1         |

| 8          | 8          | DGND         |

| 9          | 9          | CSB          |

| 10         | 10         | SCK          |

| 11         | 11         | SI           |

| 12         | 12         | SO           |

| 13         | 13         | CBUSYB       |

| 14         | 14         | DGND         |

| 15         | 15         | XT           |

| 16         | 16         | XTB          |

| 17         | 17         | DVDD         |

| 18         | 18         | NC           |

| 19         | 19         | DGND         |

| 20         | 20         | NC           |

| 21         | 21         | VDDL         |

| 22         | 22         | DVDD         |

| 23         | 23         | VDDR         |

| 24         | 24         | TESTI1(VPP)  |

| 25         | 25         | SG           |

| 26         | 26         | DGND         |

| 27         | 27         | SPVDD        |

| 28         | 28         | SPGND        |

| 29         | 29         | SPP          |

| 30         | 30         | SPM          |

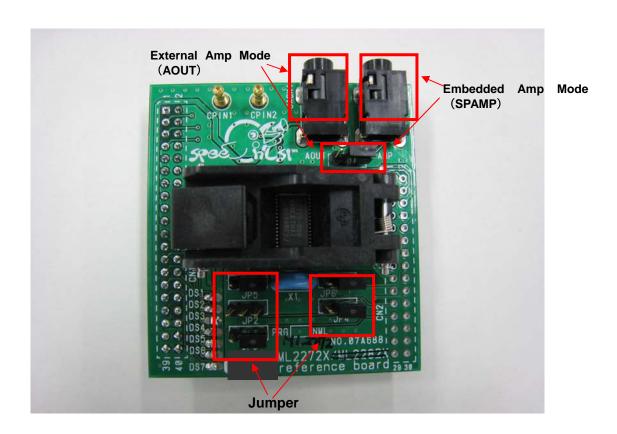

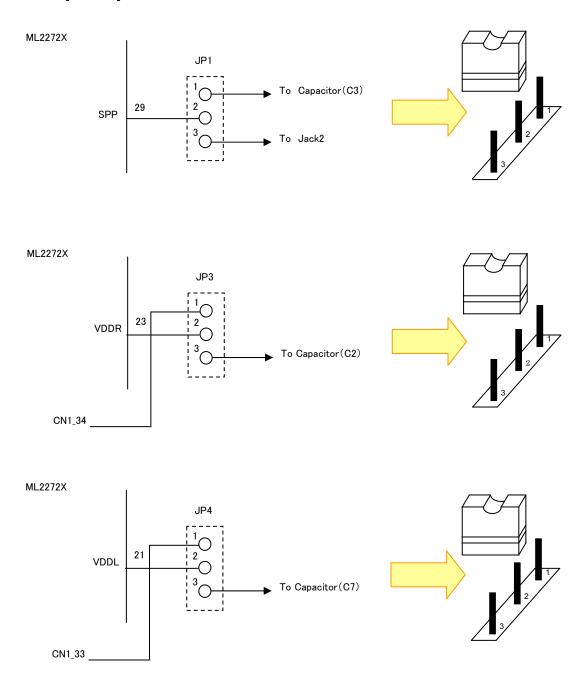

#### 3.6 Jumper specifications

Figure 4, JP1/JP3/JP4 pattern

## 3.7 Jumper Pin Setting

#### ① AMP

| Jumper Pin No. | SPAMP                   | AOUT                   |

|----------------|-------------------------|------------------------|

| JP1            | Fixed on the right side | Fixed on the left side |

#### ② Playback/Write

| Jumper Pin No. | Play                    | Write / Verify          |                        |

|----------------|-------------------------|-------------------------|------------------------|

|                | 3.3V                    | 5.0V                    | vviile / veilly        |

| JP2            | Open                    | Open                    | Open                   |

| JP3            | Fixed on the left side  | Fixed on the right side | Fixed on the left side |

| JP4            | Fixed on the right side |                         | Fixed on the left side |

| JP5            | Fixed on the right side |                         | Fixed on the left side |

| JP6            | Fixed on th             | Fixed on the left side  |                        |

#### **Revision History**

|              |            | Page                |                    |                                                                  |

|--------------|------------|---------------------|--------------------|------------------------------------------------------------------|

| Revision NO. | Date       | Previous<br>Edition | Current<br>Edition | Description                                                      |

| 1            | 2008.10.20 | _                   | _                  | Preliminary edition 1                                            |

|              |            | 1                   | 1                  | Change Notice Number :<br>NOTICE1-9 -> NOTICE1-8                 |

|              |            | _                   | _                  | 2007/2008 -> 2009                                                |

|              |            | 5                   | 5                  | Change the Pin Name : TEST -> TESTI0  VPP->TESTI1(VPP)           |

|              |            |                     |                    | Change LSI Name :<br>ML2272X/ML2282X -> ML2272X                  |

|              |            |                     |                    | Add the Text (Figure1)                                           |

|              |            | 6                   | 6                  | Change the Product Name :  ML2272X/ML2282X -> ML2272X            |

|              |            |                     |                    | Add the Text (Figure2)                                           |

|              |            |                     |                    | CN1 Pin No 1-7,20-22,32,36,38,39<br>Change the Connect LSI Name: |

|              |            |                     |                    | ML2272X/ML2282X -> ML2272X                                       |

|              |            |                     |                    | CN1 Pin No 2,32 :                                                |

|              |            |                     |                    | Change the LSI Pin Name: TEST -> TESTI0  VPP->TESTI1(VPP)        |

|              |            |                     |                    | CN1 Pin No 25-31 :                                               |

|              |            |                     |                    | Change the text (Board Select -> Device Select)                  |

|              |            | 7                   | 7                  | Fixed condition is specified                                     |

|              |            |                     |                    | CN1 Pin No 33                                                    |

| 4            | 2009.8.11  |                     |                    | Change the Connect LSI Name (> JP4)                              |

|              |            |                     |                    | Change the LSI Pin No (> 1 )                                     |

|              |            |                     |                    | CN1 Pin No 34                                                    |

|              |            |                     |                    | Change the Connect LSI Name (> JP3) Change the LSI Pin No (> 1)  |

|              |            |                     |                    | Change the LSI Pin Name (DVDD -> - )                             |

|              |            |                     |                    | CN1 Pin No 35                                                    |

|              |            |                     |                    | Change the Connect LSI Name (> ML2272X)                          |

|              |            |                     |                    | Change the LSI Pin No (> 17,22 )                                 |

|              |            |                     |                    | Change the LSI Pin Name (> DVDD)                                 |

|              |            |                     |                    | CN1 Pin No 37                                                    |

|              |            |                     |                    | Change the LSI Pin No (6 -> 1,6)                                 |

|              |            |                     |                    | Change the LSI Pin Name ( VDD -> ShutDown, VDD)                  |

|              |            |                     |                    | Change the Product Name :  ML2272X/ML2282X -> ML2272X            |

|              |            | 8                   | 8                  | CN1 Pin No 2,24                                                  |

|              |            |                     |                    | Change the LSI Pin Name : TEST -> TESTI0  VPP->TESTI1(VPP)       |

|              |            |                     |                    | Add the Text (Figure3)                                           |

|              |            |                     |                    | Change the Product Name :  ML2272X/ML2282X -> ML2272X            |

|              |            | 9                   | 9                  | Add the Text (Figure4)                                           |

| 5            | 2011.2.2   | 3                   | 3                  | Add to operating suggestions                                     |

# ML2272X Reference Board User's Manual

Issue Date: February 2, 2011

**Revision: 5**

©2011 LAPIS SEMICONDUCTOR CO.,LTD.