#### Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

#### Dear customer

LAPIS Semiconductor Co., Ltd. ("LAPIS Semiconductor"), on the 1<sup>st</sup> day of October, 2020, implemented the incorporation-type company split (shinsetsu-bunkatsu) in which LAPIS established a new company, LAPIS Technology Co., Ltd. ("LAPIS Technology") and LAPIS Technology succeeded LAPIS Semiconductor's LSI business.

Therefore, all references to "LAPIS Semiconductor Co., Ltd.", "LAPIS Semiconductor" and/or "LAPIS" in this document shall be replaced with "LAPIS Technology Co., Ltd."

Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

LAPIS Technology Co., Ltd.

October 1, 2020

# ML62Q1200A Group User's Manual

Issue Date: Feb 8, 2019

#### Notes

- 1) The information contained herein is subject to change without notice.

- 2) Although LAPIS Semiconductor is continuously working to improve product reliability and quality, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury or fire arising from failure, please take safety measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. LAPIS Semiconductor shall have no responsibility for any damages arising out of the use of our Products beyond the rating specified by LAPIS Semiconductor.

- 3) Examples of application circuits, circuit constants and any other information contained herein are provided only to illustrate the standard usage and operations of the Products. The peripheral conditions must be taken into account when designing circuits for mass production.

- 4) The technical information specified herein is intended only to show the typical functions of the Products and examples of application circuits for the Products. No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Semiconductor or any third party with respect to the information contained in this document; therefore LAPIS Semiconductor shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (i.e. AV/OA devices, communication, consumer systems, gaming/entertainment sets) as well as the applications indicated in this document.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) For use of our Products in applications requiring a high degree of reliability (as exemplified below), please contact and consult with a LAPIS Semiconductor representative: transportation equipment (i.e. cars, ships, trains), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems.

- 8) Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters.

- 9) LAPIS Semiconductor shall have no responsibility for any damages or injury arising from non-compliance with the recommended usage conditions and specifications contained herein.

- 10) LAPIS Semiconductor has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Semiconductor does not warrant that such information is error-free and LAPIS Semiconductor shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 11) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. For more details, including RoHS compatibility, please contact a ROHM sales office. LAPIS Semiconductor shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 12) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 13) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Semiconductor.

Copyright 2017-2019 LAPIS Semiconductor Co., Ltd.

#### LAPIS Semiconductor Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan http://www.lapis-semi.com/en/

FEUL62Q1200A i

#### **Preface**

This manual describes the operation of the hardware of the 16-bit microcontroller ML62Q1200A Group.

The following manuals are also available. Read them as necessary.

- nX-U16/100 Core Instruction Manual Description on the basic architecture and the each instruction of the nX-U16/100 Core.

- MACU8 Assembler Package User's Manual Description on the method of operating the relocatable assembler, the librarian, and the object converter and also on the specifications of the assembler language.

- CCU8 User's Manual Description on the method of operating the compiler.

- CCU8 Programming Guide

Description on the method of programming.

- CCU8 Language Reference

Description on the language specifications.

- DTU8 Debugger User's Manual Description on the method of operating the debugger DTU8.

- IDEU8 User's Manual Description on the integrated development environment IDEU8.

- EASE1000 User's Manual Description on the on-chip debug emulator EASE1000.

- MWuEASE Flash Writer Host Program User's Manual Description on the Flash Writer host program.

FEUL62Q1200A ii

#### **Notation**

| Classification  | Notation                                                                                                 | Description                                                                                                                                                                                                          |

|-----------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ◆ Numeric value | xxh, xxH<br>xxb                                                                                          | Indicates a hexadecimal number. x: Any value in the range of 0 to F Indicates a binary number; "b" may be omitted. x: A value 0 or 1                                                                                 |

| ♦ Unit          | word, W byte, B nibble, N mega-, M kilo-, K kilo-, k milli-, m micro-, µ nano-, n second, s (lower case) | 1 word = 16 bits<br>1 byte = 8 bits<br>1 nibble = 4 bits<br>$10^6$<br>$2^{10} = 1024$<br>$10^3 = 1000$<br>$10^{-3}$<br>$10^{-6}$<br>$10^{-9}$<br>second                                                              |

| ◆ Terminology   | "H" level "L" level                                                                                      | Indicates high voltage signal levels $V_{IH}$ and $V_{OH}$ as specified by the electrical characteristics. Indicates low voltage signal levels $V_{IL}$ and $V_{OL}$ as specified by the electrical characteristics. |

#### ♦ Register description

<sup>&</sup>quot;-" means an invalid bit. This bit returns "0" for read and write to this bit is ignored, unless otherwise specified.

FEUL62Q1200A iii

<sup>&</sup>quot;R/W" indicates that Read/Write attribute. "R" indicates that data can be read and "W" indicates that data can be written. "R/W" indicates that data can be read or written.

## Table of Contents

Chapter 1

| 1. Over   | vier                                                               | 1-1  |

|-----------|--------------------------------------------------------------------|------|

|           | atures                                                             |      |

|           | OCK DIAGRAM                                                        |      |

| 1.2.1     | Block Diagram of ML62Q1200A Group                                  |      |

| 1.3 PI    | N                                                                  |      |

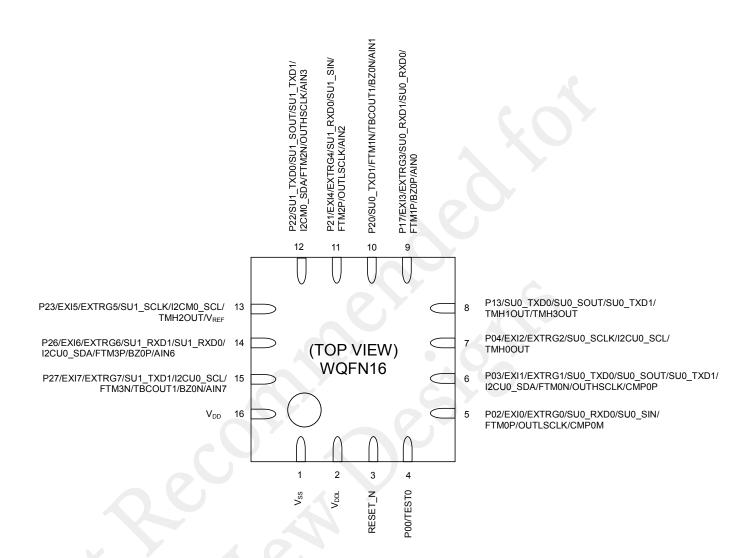

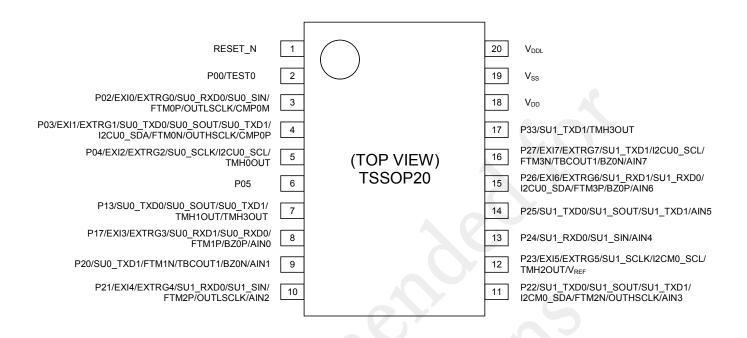

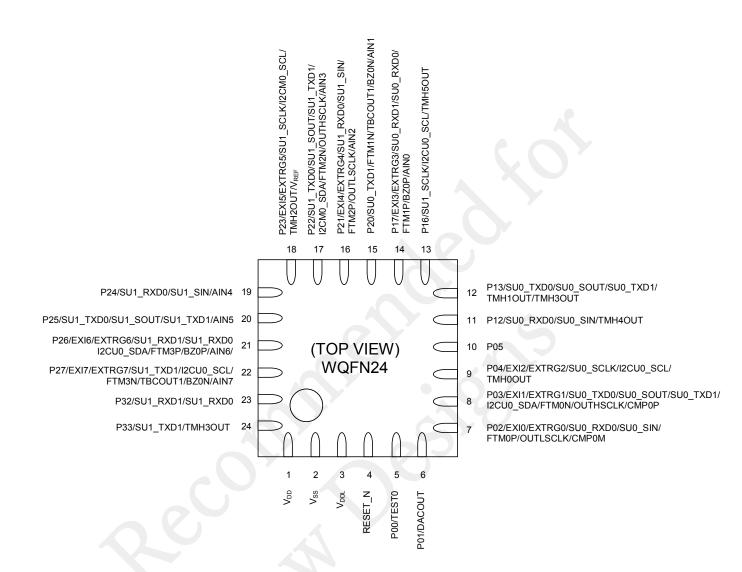

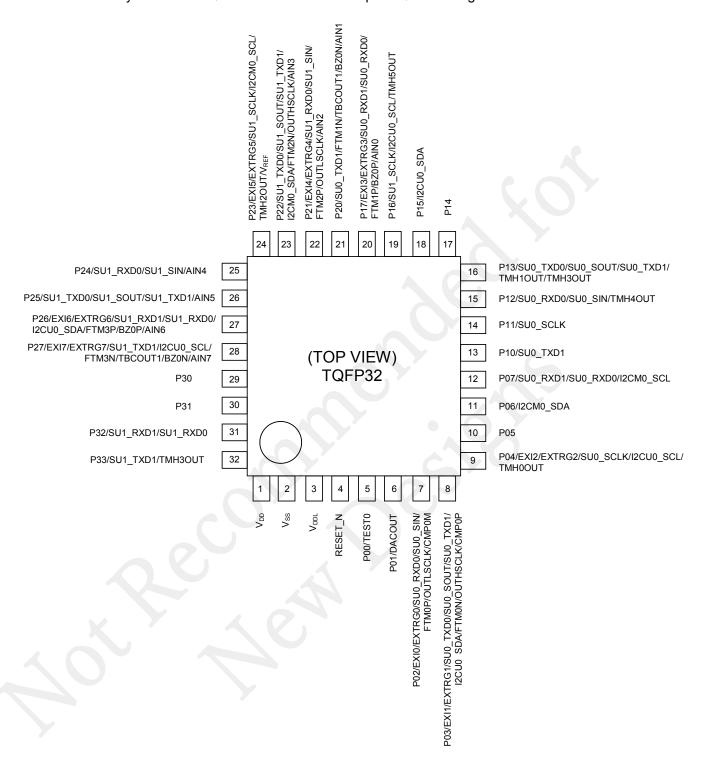

| 1.3.1     | Pin Layout                                                         |      |

| 1.3.1     | · · · · · · · · · · · · · · · · · · ·                              |      |

| 1.3.1     | •                                                                  |      |

| 1.3.1     | •                                                                  |      |

| 1.3.1     |                                                                    |      |

| 1.3.1     |                                                                    |      |

| 1.3.2     | PIN LIST.                                                          |      |

| 1.3.3     | PIN DESCRIPTION                                                    |      |

| 1.3.4     | TERMINATION OF UNUSED PINS                                         |      |

|           |                                                                    |      |

| Chapter 2 |                                                                    |      |

| 2 CDII    | IM C                                                               | 2.1  |

|           | and Memory Space                                                   |      |

|           | eneral Description                                                 |      |

|           | PU nX-U16/100                                                      |      |

| 2.2.1     | Wait mode and No wait mode                                         |      |

|           | pprocessor                                                         |      |

| 2.3.1     | Multiplication/Division                                            |      |

| 2.3.2     | List of Registers                                                  |      |

|           | A, B, C, D Registers (CR0 to CR7)                                  |      |

|           | 2.2 Operation Mode Register (CR8), Operation Status Register (CR9) |      |

|           | .3 Coprocessor ID Register (CR15)                                  |      |

| 2.3.3     | Description of Operation                                           |      |

|           | ogram Memory Space                                                 |      |

|           | ata Memory Space                                                   |      |

|           | escription of Registers                                            |      |

| 2.6.1     | List of Registers                                                  |      |

| 2.6.2     | Data Segment Register (DSR)                                        |      |

| 2.6.3     |                                                                    |      |

| 2.7 Sc    | ftware Remap Function                                              | 2-24 |

| CI (      |                                                                    |      |

| Chapter 3 |                                                                    |      |

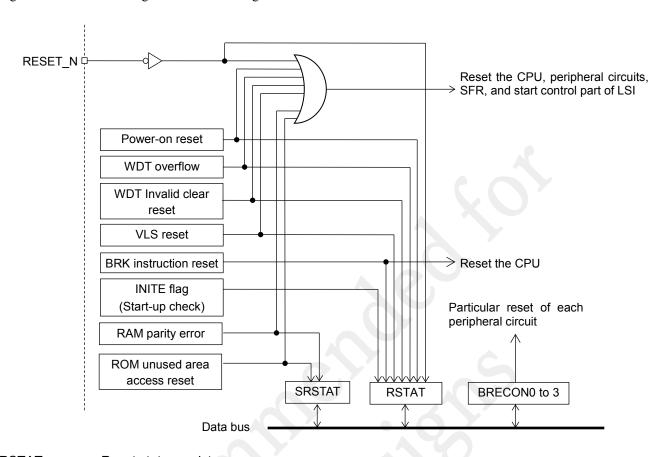

| 3. Rese   | t Function                                                         | 3-1  |

|           | eneral Description                                                 |      |

| 3.1.1     | Features                                                           |      |

| 3.1.2     | Configuration                                                      |      |

| 3.1.3     | List of Pins                                                       |      |

|           | escription of Registers                                            |      |

| 3.2.1     | List of Registers                                                  |      |

| 3.2.2     | Reset Status Register (RSTAT)                                      |      |

| 3.2.3     | Safety Function Reset Status Register (SRSTAT)                     | 3-5  |

|           | escription of Operation                                            |      |

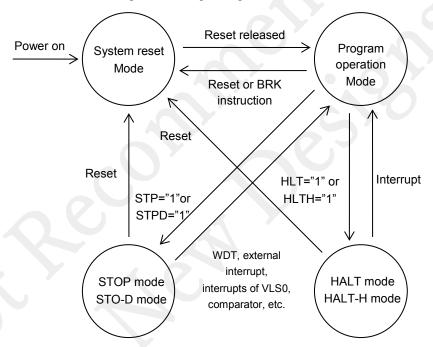

| 3.3.1     | Operation in Reset Mode                                            |      |

| 3.3.2     | Operation of System Reset Mode                                     |      |

| 3.3.3     | RESET N pin                                                        |      |

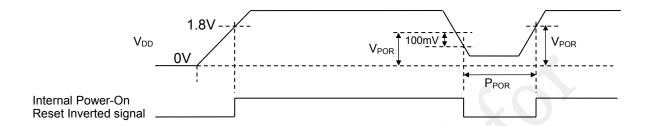

| 3.3.4     | Power-On Reset                                                     |      |

## Chapter 4

|           | r Management                                    |      |

|-----------|-------------------------------------------------|------|

|           | neral Description                               |      |

| 4.1.1     | Features                                        |      |

| 4.1.2     | Configuration                                   |      |

|           | scription of Registers                          |      |

| 4.2.1     | List of Registers                               |      |

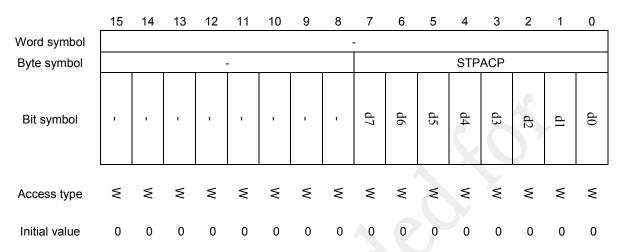

| 4.2.2     | Stop Code Acceptor (STPACP)                     |      |

| 4.2.3     | Standby Control Register (SBYCON)               |      |

| 4.2.4     | Block Clock Control Register 0 (BCKCON0)        |      |

| 4.2.5     | Block Clock Control Register 1 (BCKCON1)        |      |

| 4.2.6     | Block Clock Control Register 2 (BCKCON2)        |      |

| 4.2.7     | Block Clock Control Register 3 (BCKCON3)        |      |

| 4.2.8     | Block Reset Control Register 0 (BRECON0)        |      |

| 4.2.9     | Block Reset Control Register 1 (BRECON1)        |      |

| 4.2.10    | Block Reset Control Register 2 (BRECON2)        |      |

| 4.2.11    | Block Reset Control Register 3 (BRECON3)        |      |

|           | scription of Operation                          |      |

| 4.3.1     | Program Run Mode                                |      |

| 4.3.2     | HALT Mode                                       |      |

| 4.3.3     | HALT-H mode                                     |      |

| 4.3.4     | STOP mode                                       |      |

| 4.3.5     | STOP-D Mode                                     |      |

| 4.3.6     | Note on Return Operation from the standby modes |      |

| 4.3.7     | Operation of Functions in the standby modes     |      |

| 4.3.8     | Block Control Function.                         | 4-20 |

| ~1        |                                                 |      |

| Chapter 5 |                                                 |      |

| 5. Intern | upts                                            | 5-1  |

| 5.1 Ge    | neral Description                               | 5-1  |

| 5.1.1     | Features                                        |      |

| 5.2 De    | scription of Registers                          |      |

| 5.2.1     | List of Registers                               |      |

| 5.2.2     | Interrupt Enable Register 01 (IE01)             |      |

| 5.2.3     | Interrupt Enable Register 23 (IE23)             |      |

| 5.2.4     | Interrupt Enable Register 45 (IE45)             |      |

| 5.2.5     | Interrupt Enable Register 67 (IE67)             |      |

| 5.2.6     | Interrupt Request Register 01 (IRQ01)           |      |

| 5.2.7     | Interrupt Request Register 23 (IRQ23)           |      |

| 5.2.8     | Interrupt Request Register 45 (IRQ45)           |      |

| 5.2.9     | Interrupt Request Register 67 (IRQ67)           |      |

| 5.2.10    | Interrupt Level Control Enable Register (ILEN)  |      |

| 5.2.11    | Current Interrupt Request Level Register (CIL)  |      |

| 5.2.12    | Interrupt Level Control Register 0 (ILC0)       |      |

| 5.2.13    | Interrupt Level Control Register 1 (ILC1)       |      |

| 5.2.14    | Interrupt Level Control Register 2 (ILC2)       |      |

| 5.2.15    | Interrupt Level Control Register 3 (ILC3)       | 5-17 |

| 5.2.16    | Interrupt Level Control Register 4 (ILC4)       |      |

| 5.2.17    | Interrupt Level Control Register 5 (ILC5)       |      |

| 5.2.18    | Interrupt Level Control Register 6 (ILC6)       |      |

| 5.2.19    | Interrupt Level Control Register 7 (ILC7)       |      |

|           | scription of Operation                          |      |

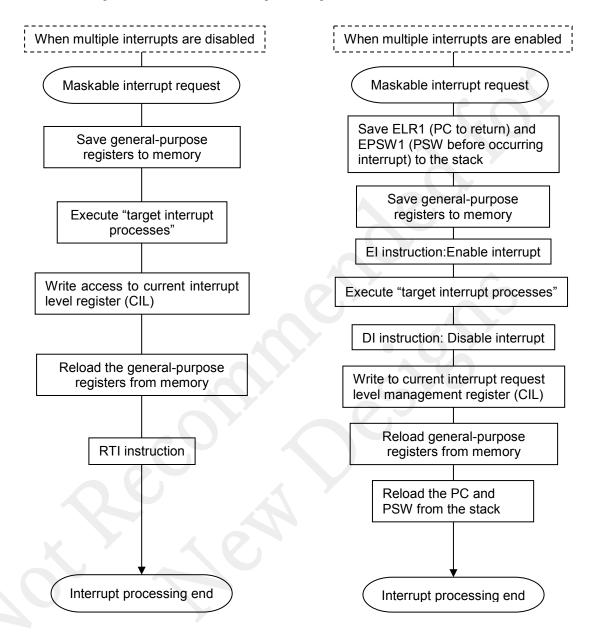

| 5.3.1     | Maskable Interrupt Processing                   |      |

| 5.3.2     |                                                 |      |

| U.U.=     | Non-Maskable Interrupt Processing               | 5-25 |

| 5.3.3     | Non-Maskable Interrupt Processing               |      |

|           |                                                 | 5-25 |

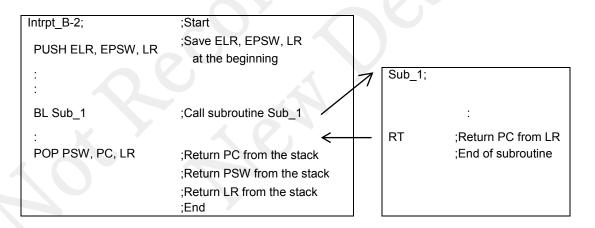

| 5.3.6          | How to program the interrupt process when the interrupt level control is enabled |                  |

|----------------|----------------------------------------------------------------------------------|------------------|

| 5.3.6          |                                                                                  |                  |

| 5.3.6          | .2 When programming interrupts defined as it enables other multiple interrupts   | 5-32             |

| 5.3.7          | Interrupt Disable State                                                          | 5-33             |

|                |                                                                                  |                  |

| Chapter 6      |                                                                                  |                  |

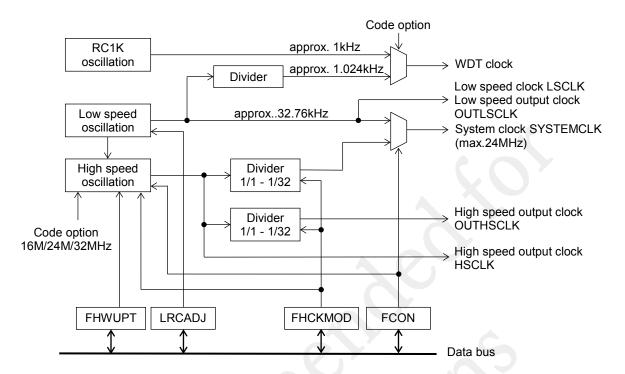

| 6. Cloc        | k Generation Circuit                                                             | 6-1              |

|                | eneral Description                                                               |                  |

| 6.1.1          | Features                                                                         |                  |

| 6.1.2          | Configuration                                                                    |                  |

| 6.1.3          | List of Pins                                                                     |                  |

|                | escription of Registers                                                          |                  |

| 6.2.1          | List of Registers                                                                |                  |

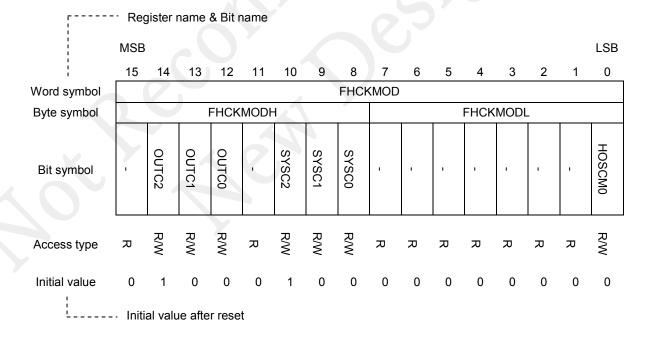

| 6.2.2          | High-Speed Clock Mode Register (FHCKMOD)                                         |                  |

| 6.2.3          | Clock Control Register (FCON)                                                    |                  |

| 6.2.4          | High-Speed Clock Wake-up Time Setting Register (FHWUPT)                          |                  |

| 6.2.5          | Low-Speed RC Oscillation Frequency Adjustment Register (LRCADJ)                  |                  |

|                | escription of Operation.                                                         |                  |

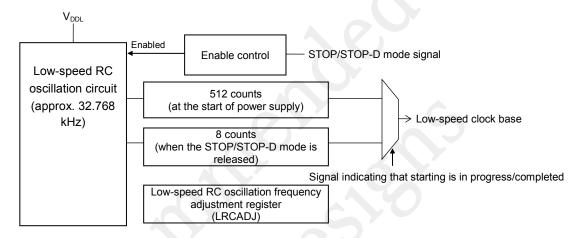

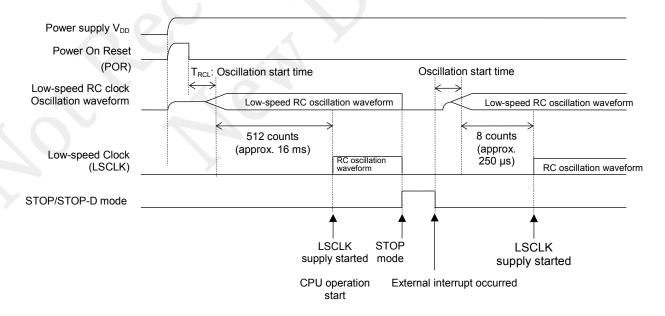

| 6.3.1          | Low-Speed Clock                                                                  |                  |

|                | ·                                                                                |                  |

| 6.3.1<br>6.3.2 |                                                                                  |                  |

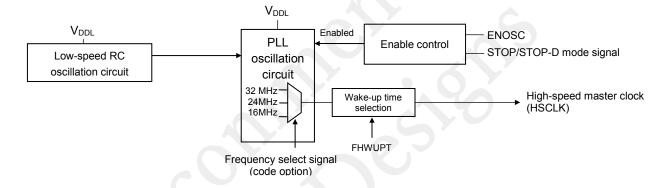

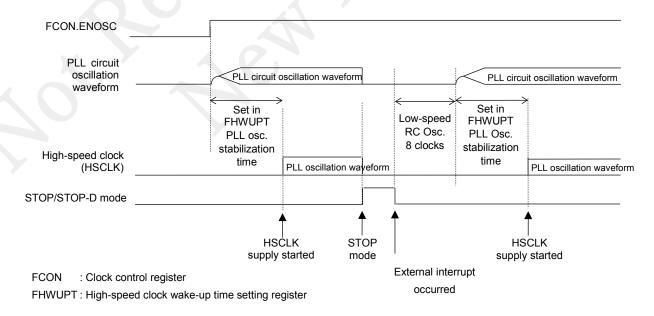

|                | High-Speed Clock                                                                 |                  |

| 6.3.2          |                                                                                  |                  |

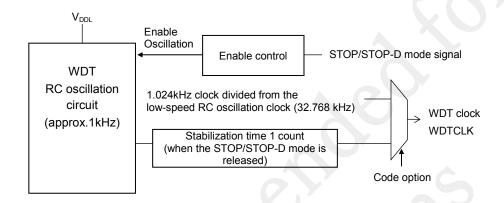

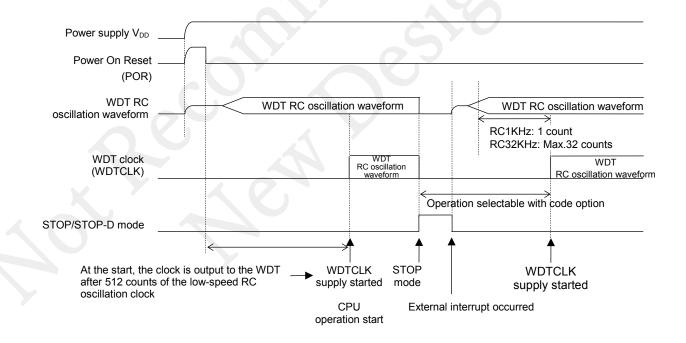

| 6.3.3          | WDT Clock                                                                        |                  |

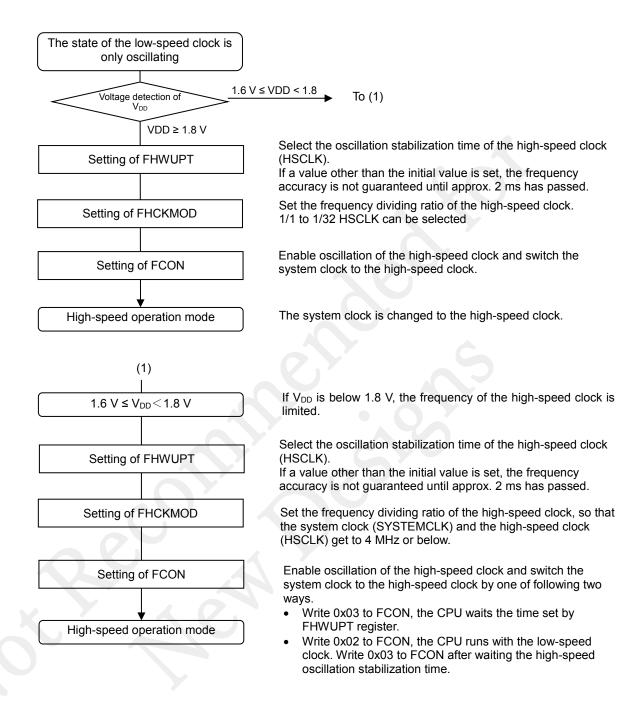

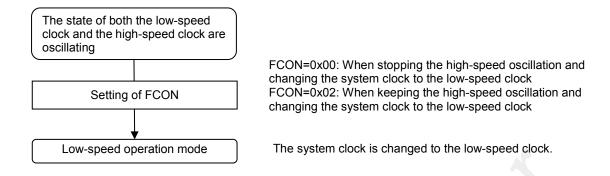

| 6.3.4          | Switching of System Clock                                                        | 6-13             |

| Chapter 7      |                                                                                  |                  |

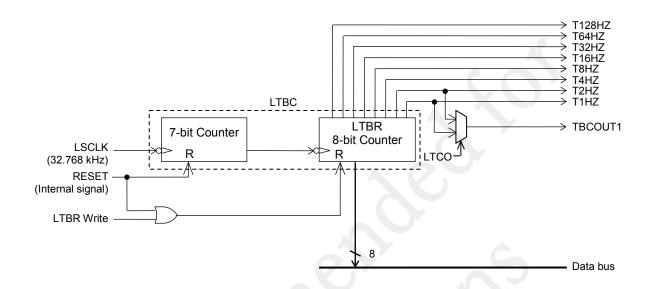

| 7. Low         | Speed Time Base Counter                                                          | 7-1              |

| 7.1 Ge         | eneral Description                                                               | 7 <sub>-</sub> 1 |

| 7.1.1          | Features                                                                         |                  |

| 7.1.2          | Configuration                                                                    |                  |

| 7.1.3          | List of Pins                                                                     |                  |

|                | escription of Registers                                                          |                  |

| 7.2.1          | List of Registers                                                                |                  |

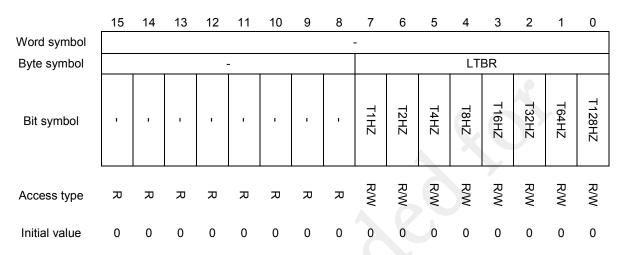

| 7.2.1          | Low Speed Time Base Counter Register (LTBR)                                      |                  |

| 7.2.2          | Low Speed Time Base Register Control Register (LTBCON)                           |                  |

| 7.2.3          | Low Speed Time Base Counter Interrupt Selection Register (LTBINT)                |                  |

|                | escription of Operation                                                          |                  |

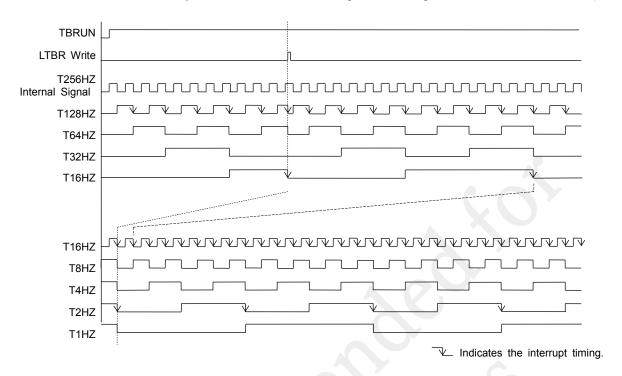

| 7.3 Do         | Operation of Low Speed Time Base Counter                                         |                  |

| 7.5.1          |                                                                                  | ,                |

| Chapter 8      |                                                                                  |                  |

| 8. 16-B        | it Timer                                                                         | 8-1              |

| 8.1 G          | eneral Description                                                               |                  |

| 8.1.1          | Features                                                                         | 8-1              |

| 8.1.2          | Configuration                                                                    | 8-1              |

| 8.1.3          | List of Pins                                                                     | 8-3              |

| 8.2 De         | escription of Registers                                                          | 8-4              |

| 8.2.1          | List of Registers                                                                | 8-4              |

| 8.2.2          | 16-Bit Timer n Data Register (TMHnD: n = 0 to 5)                                 |                  |

| 8.2.3          | 16-Bit Timer n Counter Register (TMHnC: n = 0 to 5)                              |                  |

| 8.2.4          | 16-Bit Timer n Mode Register (TMHnMOD: n = 0 to 5)                               |                  |

| 8.2.5          | 16-Bit Timer n Interrupt Status Register (TMHnIS: n = 0 to 5)                    |                  |

| 8.2.6          | 16-Bit Timer n Interrupt Clear Register (TMHnIC: n = 0 to 5)                     |                  |

| 8.2.7          | 16-Bit Timer Start Register (TMHSTR)                                             |                  |

| 8.2.8          | 16-Bit Timer Stop Register (TMHSTP)                                              |                  |

| 8.2.9          | 16-Bit Timer Status Register (TMHSTAT)                                           |                  |

|                | escription of Operation.                                                         |                  |

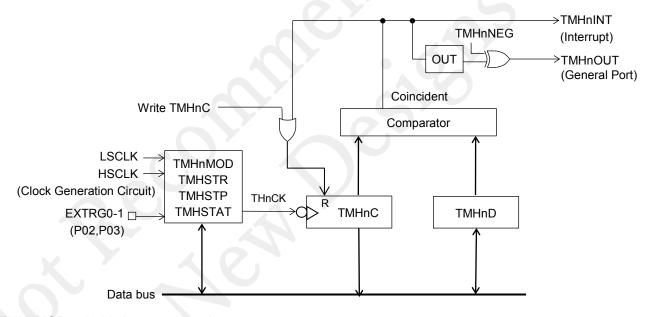

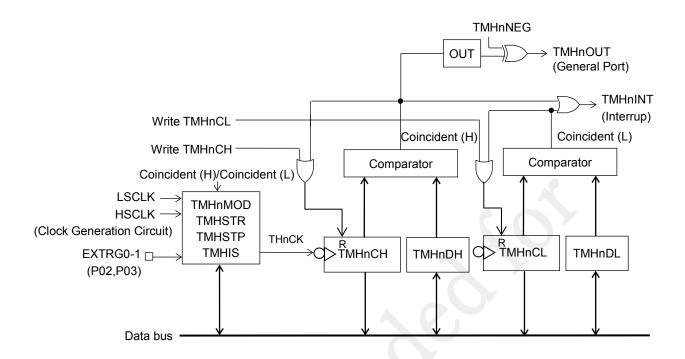

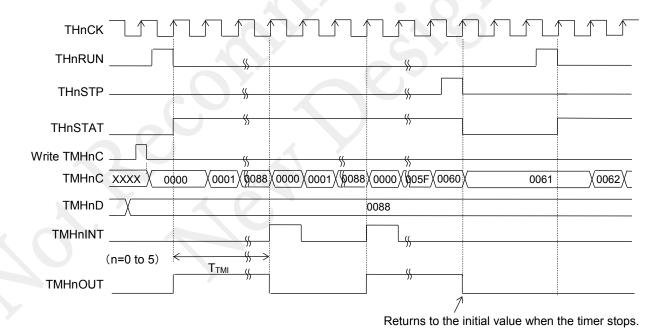

| 8.3.1          | Basic Operation of 16-Bit Timer                                                  |                  |

| MII 60010      | •                                                                                | C 4 4 9          |

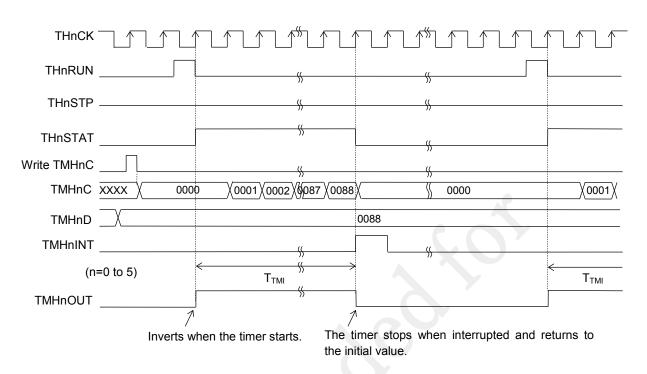

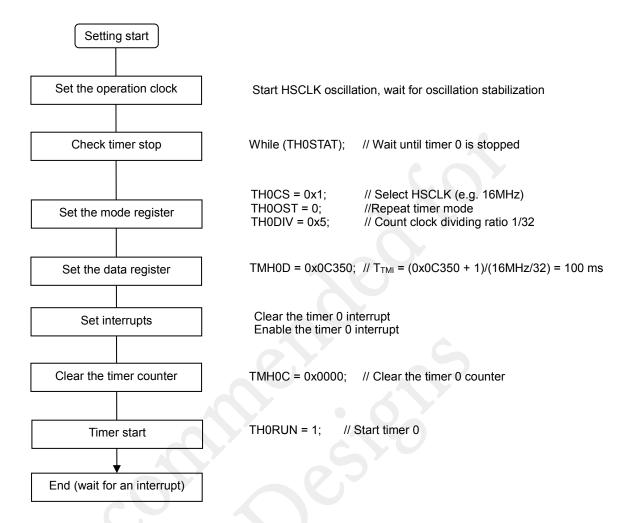

| 8.3.2            | Setting Example of Repeat Timer Mode.                                                       |                           |

|------------------|---------------------------------------------------------------------------------------------|---------------------------|

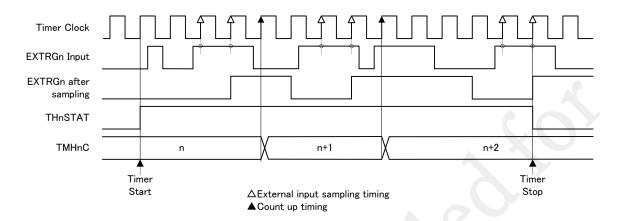

| 8.3.3            | External Input Count Timing                                                                 | 8-21                      |

| Chapter 9        |                                                                                             |                           |

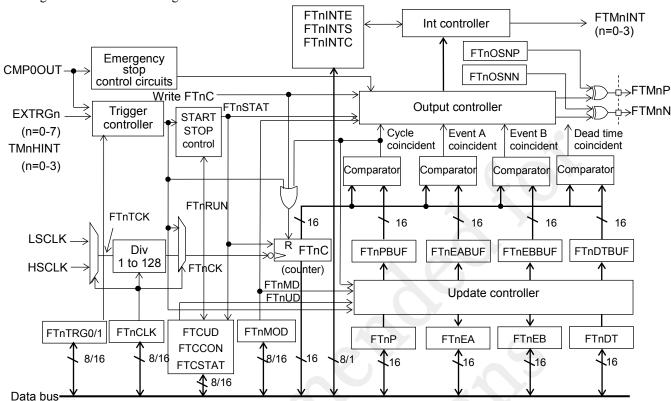

| 9. FUN           | CTIONAL TIMER (FTM)                                                                         | 9-1                       |

|                  | neral Description                                                                           |                           |

| 9.1.1            | Features                                                                                    |                           |

| 9.1.2            | Configuration                                                                               |                           |

| 9.1.3            | List of Pins                                                                                |                           |

|                  | scription of Registers                                                                      |                           |

| 9.2.1            | List of Registers                                                                           |                           |

| 9.2.2<br>9.2.3   | FTMn Cycle Register (FTnP: n = 0, 1, 2, 3)<br>FTMn Event Register A (FTnEA: n = 0, 1, 2, 3) |                           |

| 9.2.3<br>9.2.4   | FTMn Event Register B (FTnEB: n = 0, 1, 2, 3)                                               |                           |

| 9.2.5            | FTMn Dead Time Register (FTnDT: n = 0, 1, 2, 3)                                             |                           |

| 9.2.6            | FTMn Counter Register (FTnC: $n = 0, 1, 2, 3$ )                                             |                           |

| 9.2.7            | FTMn Status Register (FTnSTAT: $n = 0, 1, 2, 3$ )                                           |                           |

| 9.2.8            | FTMn Mode Register (FTnMOD: n = 0, 1, 2, 3)                                                 |                           |

| 9.2.9            | FTMn Clock Register (FTnCLK: n=0,1,2,3)                                                     |                           |

| 9.2.10           | FTMn Trigger Register 0 (FTnTRG0: n = 0, 1, 2, 3)                                           | 9-19                      |

| 9.2.11           | FTMn Trigger Register 1 (FTnTRG1: n = 0, 1, 2, 3)                                           |                           |

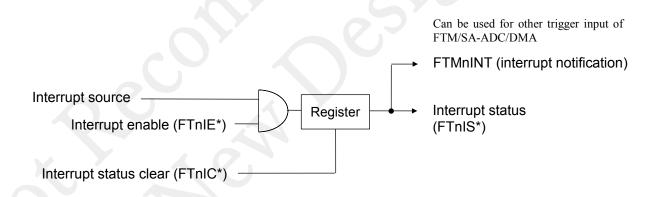

| 9.2.12           | FTMn Interrupt Enable Register (FTnINTE: n = 0, 1, 2, 3)                                    |                           |

| 9.2.13           | FTMn Interrupt Status Register (FTnINTS: n = 0, 1, 2, 3)                                    |                           |

| 9.2.14           | FTMn Interrupt Clear Register (FTnINTC: n = 0, 1, 2, 3)                                     |                           |

| 9.2.15           | FTM Common Update Register (FTCUD)                                                          |                           |

| 9.2.16           | FTM Common Control Register (FTCCON)                                                        |                           |

| 9.2.17<br>9.2.18 | FTM Common Start Register (FTCSTR)                                                          | 9-31<br>0 22              |

| 9.2.18           | FTM Stop Register (FTCSTF)                                                                  | 9-32<br>9 <sub>-</sub> 33 |

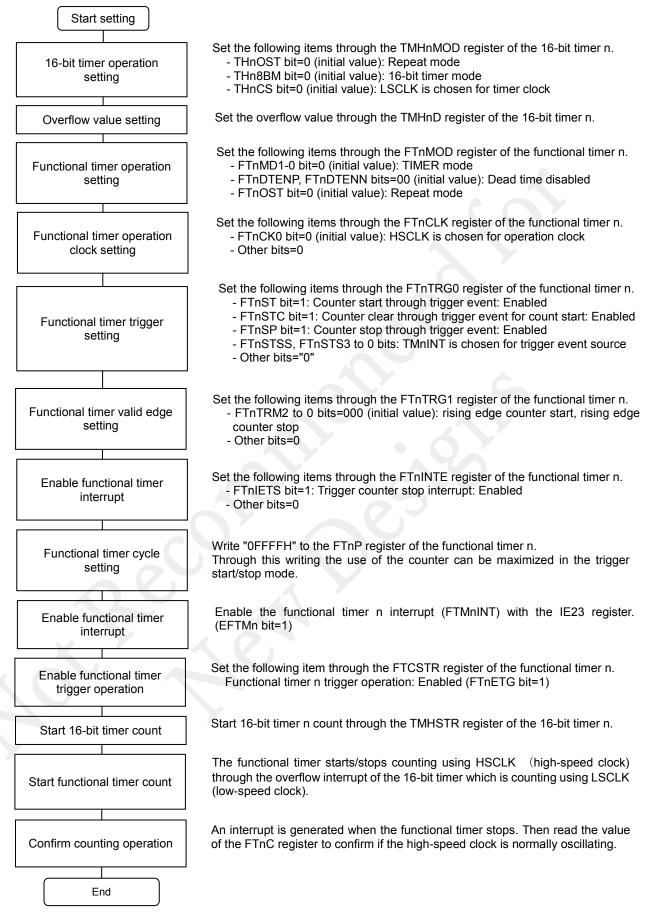

|                  | scription of Operation                                                                      |                           |

| 9.3.1            | Common Sequence                                                                             |                           |

| 9.3.2            | Counter Operation.                                                                          |                           |

| 9.3.2.           | •                                                                                           |                           |

| 9.3.2.           |                                                                                             |                           |

| 9.3.3            | TIMER Mode Operation                                                                        | 9-37                      |

| 9.3.3.           |                                                                                             |                           |

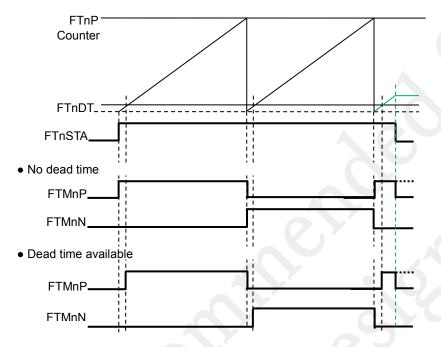

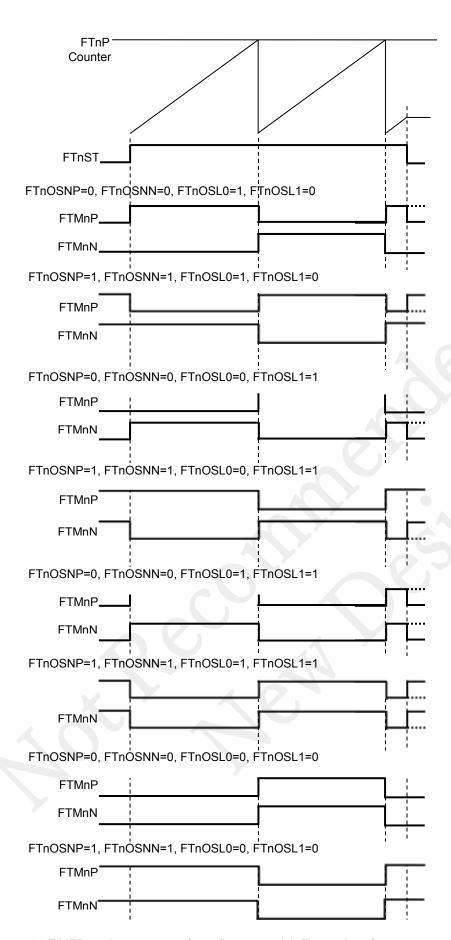

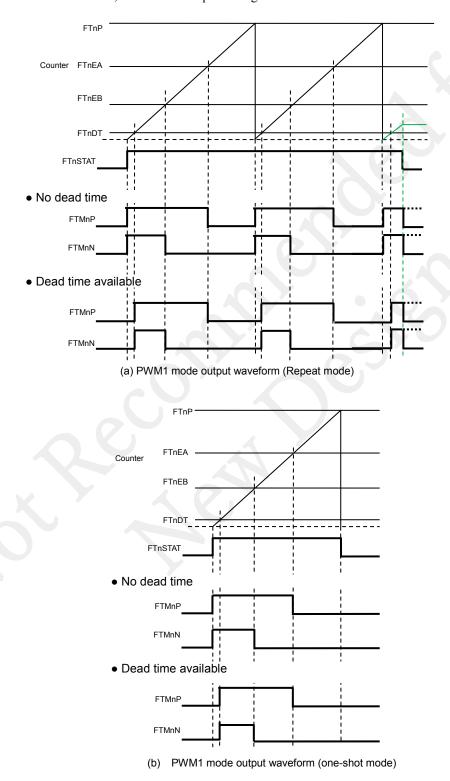

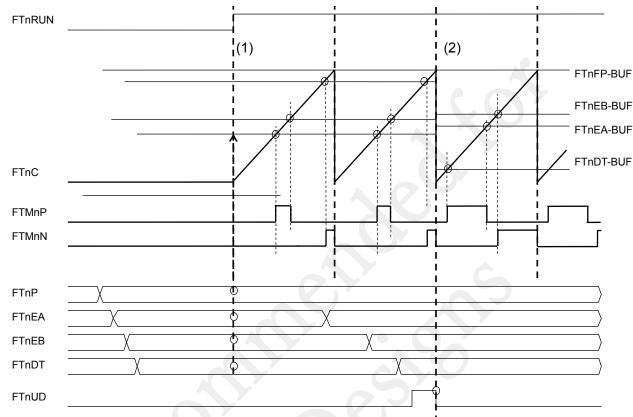

| 9.3.4            | PWM1 Mode Operation                                                                         |                           |

|                  | 1 Output Waveform in PWM1 Mode                                                              |                           |

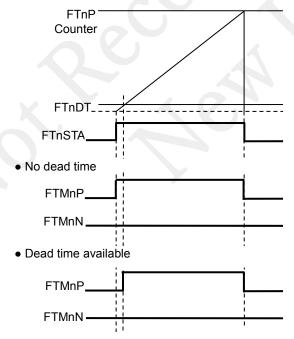

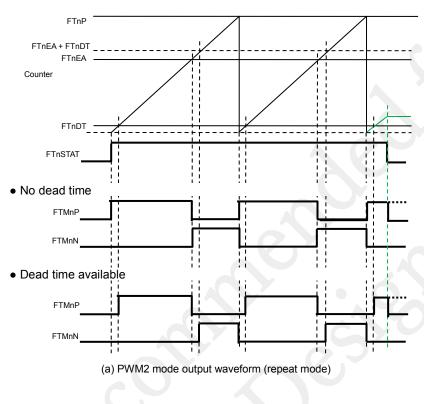

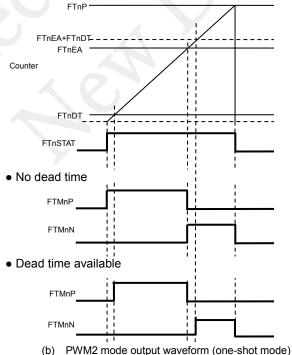

|                  | PWM2 Mode Operation                                                                         |                           |

| 9.3.5.           |                                                                                             |                           |

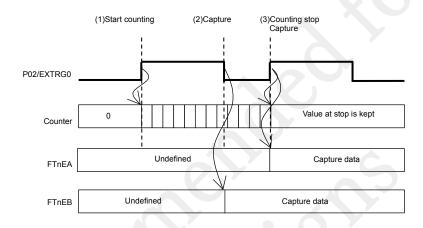

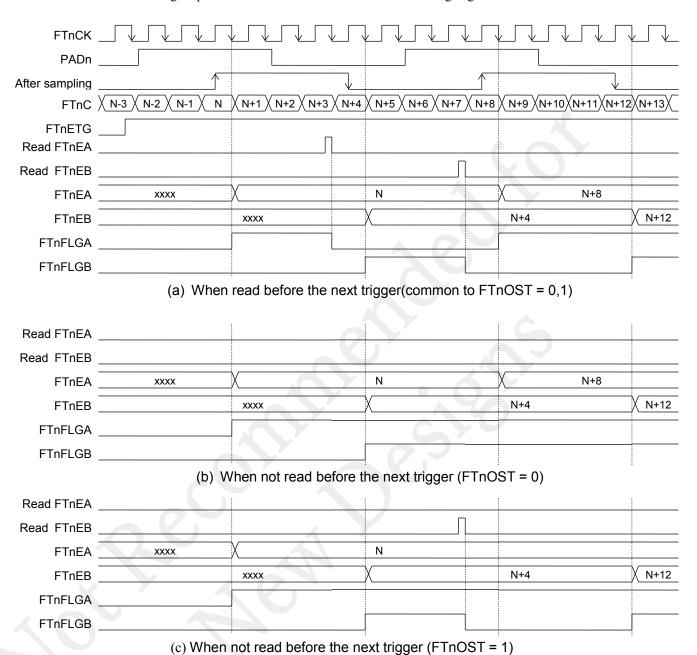

| 9.3.6<br>9.3.6.  | CAPTURE Mode Operation                                                                      |                           |

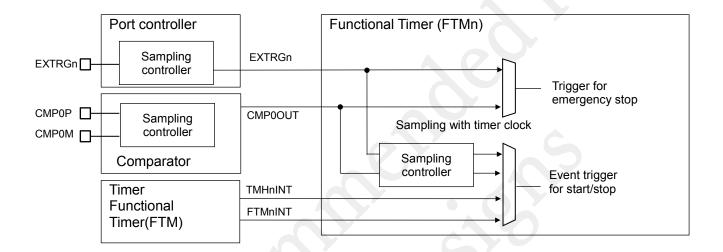

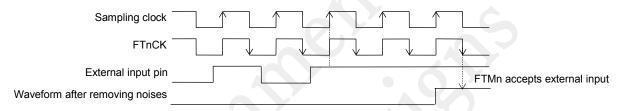

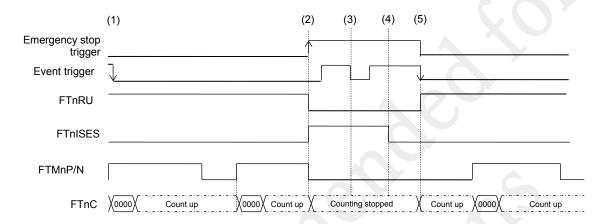

| 9.3.0.           | Event/Emergency Stop Trigger Control                                                        |                           |

| 9.3.7.           |                                                                                             |                           |

| 9.3.7.           |                                                                                             |                           |

| 9.3.7.           | 1 1 5 66                                                                                    |                           |

| 9.3.8            | Emergency Stop Operation                                                                    |                           |

| 9.3.9            | Changing Cycle, Event A/B, and Dead Time during Operation                                   |                           |

| 9.3.10           | Interrupt Source                                                                            | 9-46                      |

| Chapter 1        | 0                                                                                           |                           |

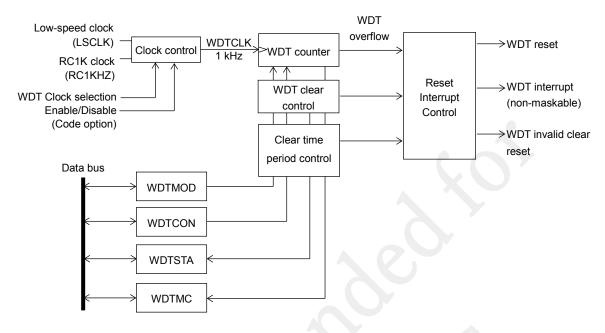

| 10. Watc         | hdog Timer                                                                                  | 10-1                      |

|                  | neral Description                                                                           |                           |

| 10.1.1           | Features                                                                                    |                           |

| 10.1.2           | Configuration                                                                               |                           |

|                  | scription of Registers                                                                      |                           |

| 10.2.1           | List of Registers                                                                           | 10-2                      |

| 10.2.2     | Watchdog Timer Control Register (WDTCON)                                    | 10-3  |

|------------|-----------------------------------------------------------------------------|-------|

| 10.2.3     | Watchdog Timer Mode Register (WDTMOD)                                       |       |

| 10.2.4     | Watchdog Timer Counter Register (WDTMC)                                     | 10-5  |

| 10.2.5     | Watchdog Status Register (WDTSTA)                                           | 10-6  |

| 10.3 Des   | scription of Operation                                                      |       |

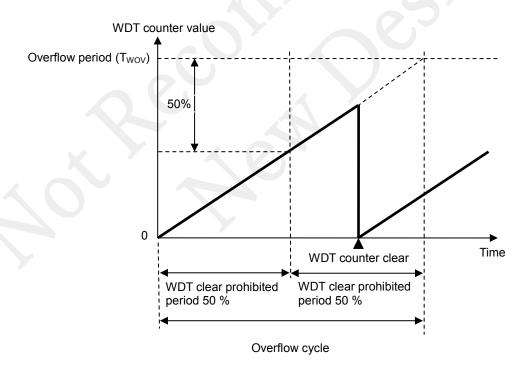

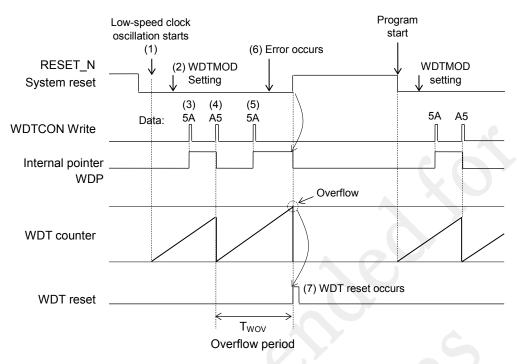

| 10.3.1     | Operation when WDT clear enable time period is 100% of overflow cycle       | 10-9  |

| 10.3.2     | Operation when WDT clear enable time period is 75% or 50% of overflow cycle | 10-11 |

| Chapter 1  | 1                                                                           |       |

| _          |                                                                             | 11.1  |

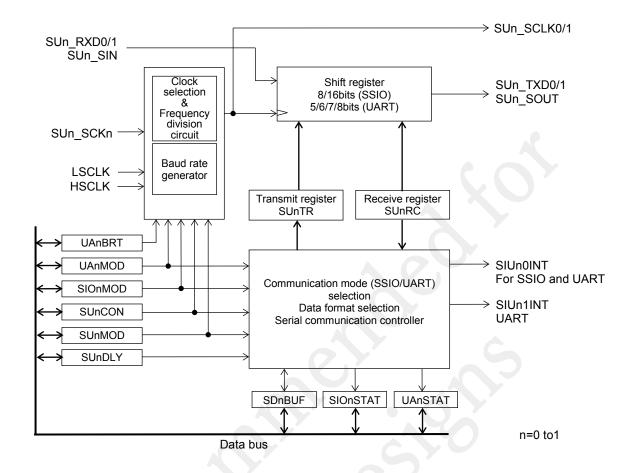

|            | Communication Unit                                                          |       |

|            | neral Description                                                           |       |

| 11.1.1     | Features                                                                    |       |

| 11.1.2     | Configuration                                                               |       |

| 11.1.3     | List of Pins                                                                |       |

|            | scription of Registers                                                      |       |

| 11.2.1     | List of Registers                                                           |       |

| 11.2.2     | Serial Unit n Transmit/Receive Buffer (SDnBUF)                              |       |

| 11.2.3     | Serial Unit n Mode Register (SUnMOD)                                        |       |

| 11.2.4     | Serial Unit n Transmission Interval Setting Register (SUnDLY)               |       |

| 11.2.5     | Serial Unit n Control Register (SUnCON)                                     |       |

| 11.2.6     | Synchronous Serial Port n Mode Register (SIOnMOD)                           |       |

| 11.2.7     | Synchronous Serial Port n Status Register (SIOnSTAT)                        |       |

| 11.2.8     | UARTn0 Mode Register (UAn0MOD)                                              |       |

| 11.2.9     | UARTn1 Mode Register (UAn1MOD)                                              |       |

|            | UART0 Baud Rate Register (UAn0BRT)                                          |       |

|            | UARTn1 Baud Rate Register (UAn1BRT)                                         |       |

|            | UARTn0 Baud Rate Adjustment Register (UAn0BRC)                              |       |

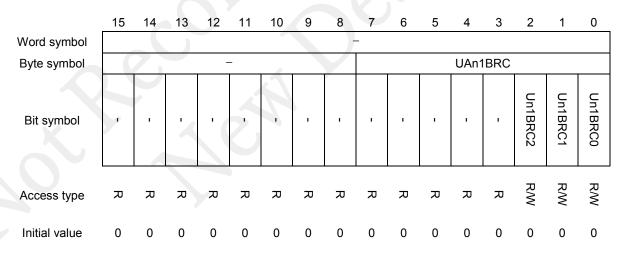

|            | UARTn1 Baud Rate Adjustment Register (UAn1BRC)                              |       |

|            | UARTn0 Status Register (UAn0STAT)                                           |       |

|            | UARTn1 Status Register (UAn1STAT)                                           |       |

|            | scription of Operation                                                      |       |

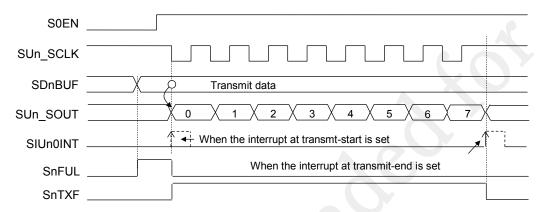

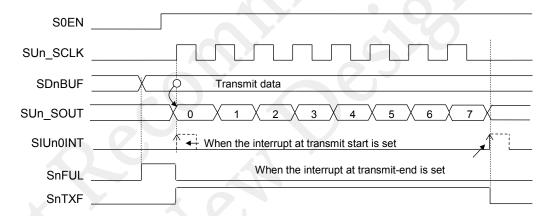

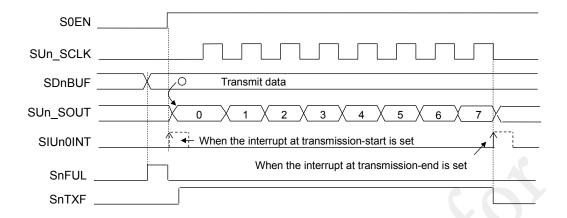

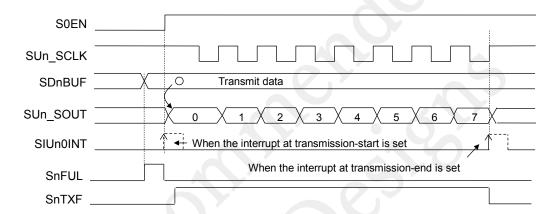

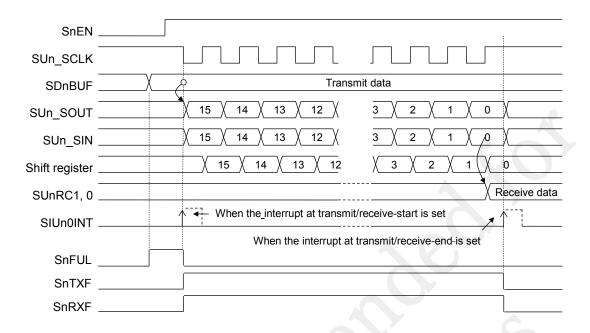

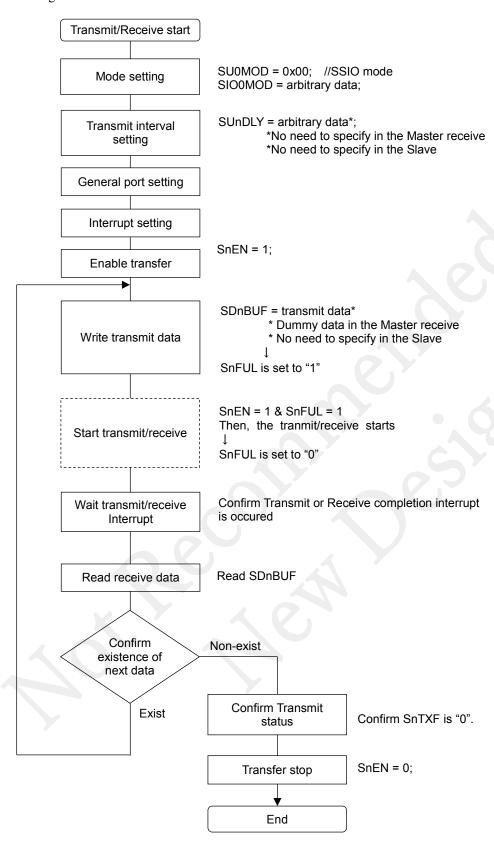

| 11.3.1     | Synchronous Serial Port (SSIO)                                              |       |

| 11.3.1     |                                                                             |       |

| 11.3.1     | S                                                                           |       |

| 11.3.1     |                                                                             |       |

| 11.3.2     |                                                                             |       |

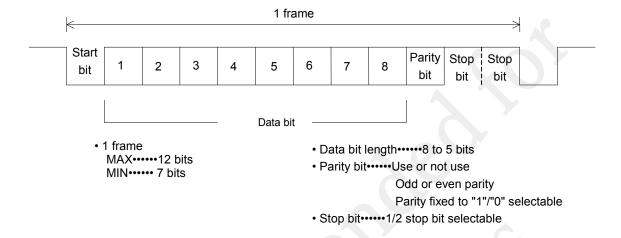

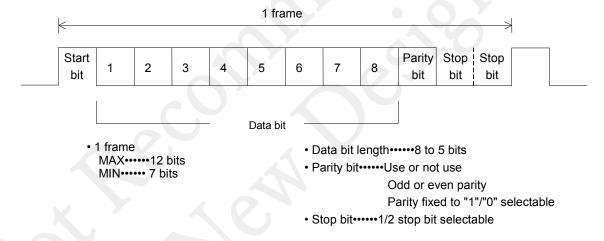

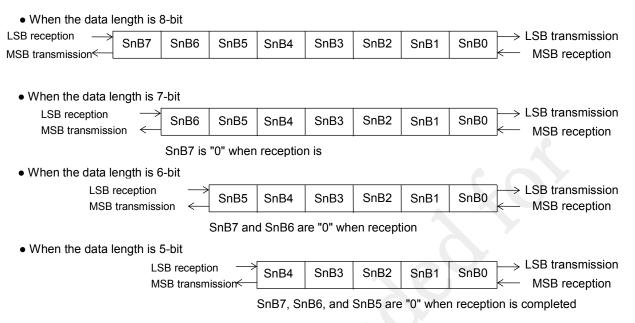

| 11.3.2     | 2.1 Transfer Data Format                                                    | 11-30 |

| 11.3.2     |                                                                             |       |

| 11.3.2     | 2.3 Transmitted Data Direction                                              | 11-32 |

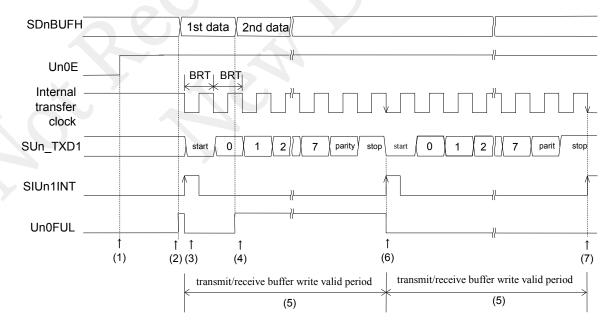

| 11.3.2     | 2.4 Transmit Operation                                                      | 11-33 |

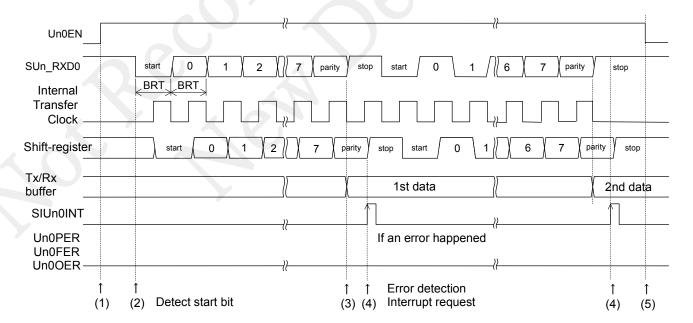

| 11.3.2     | 2.5 Receive Operation                                                       | 11-34 |

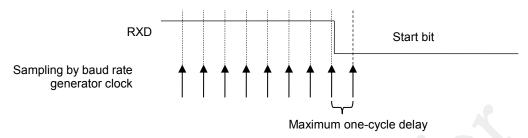

| 11.3.2     | 2.6 Detection of Start Bit                                                  | 11-35 |

| 11.3.2     |                                                                             |       |

| 11.3.2     | 2.8 Receive Margin                                                          | 11-36 |

| 11.3.3     | Pin Settings                                                                | 11-37 |

| Chapter 12 | 2                                                                           |       |

|            |                                                                             | 10.1  |

|            | dus Unit                                                                    |       |

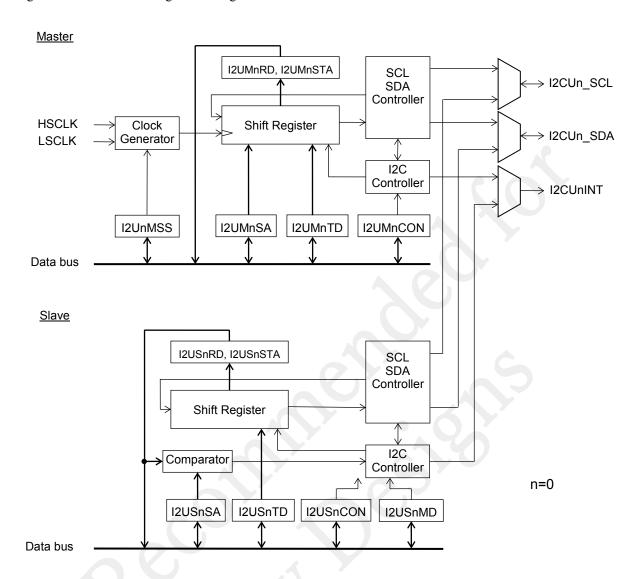

|            | neral Description                                                           |       |

| 12.1.1     | Features                                                                    |       |

| 12.1.2     | Configuration                                                               |       |

| 12.1.3     | List of Pins                                                                |       |

|            | scription of Registers                                                      |       |

| 12.2.1     | List of Registers                                                           |       |

| 12.2.2     | I2C Bus Unit 0 Mode Register (I2U0MSS)                                      |       |

| 12.2.3     | I2C Bus 0 Receive Register (Master) (I2UM0RD)                               |       |

| 12.2.4     | I2C Bus 0 Slave Address Register (Master) (I2UM0SA)                         | 12-6  |

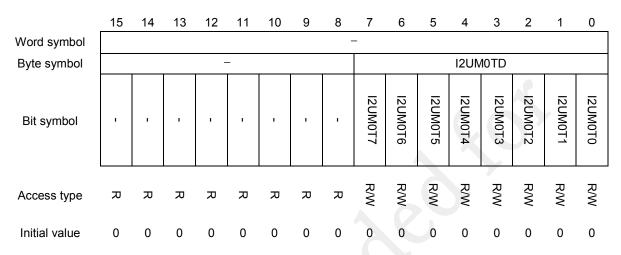

| 12.2.5           | I2C Bus 0 Transmit Data Register (Master) (I2UM0TD) | 12-7  |

|------------------|-----------------------------------------------------|-------|

| 12.2.6           | I2C Bus 0 Control Register (Master) (I2UM0CON)      |       |

| 12.2.7           | I2C Bus 0 Mode Register (Master) (I2UM0MOD)         |       |

| 12.2.8           | I2C Bus 0 Status Register (Master) (I2UM0STA)       |       |

| 12.2.9           | I2C Bus 0 Receive Register (Slave) (I2US0RD)        |       |

| 12.2.10          | I2C Bus 0 Slave Address Register (Slave) (I2US0SA)  |       |

| 12.2.11          | I2C Bus 0 Transmit Data Register (Slave) (I2US0TD)  | 12-15 |

| 12.2.12          | I2C Bus 0 Control Register (Slave) (I2US0CON)       | 12-16 |

| 12.2.13          | I2C Bus 0 Mode Register (Slave) (I2US0MD)           | 12-17 |

|                  | I2C Bus 0 Status Register (Slave) (I2US0STA)        |       |

|                  | cription of Operation                               |       |

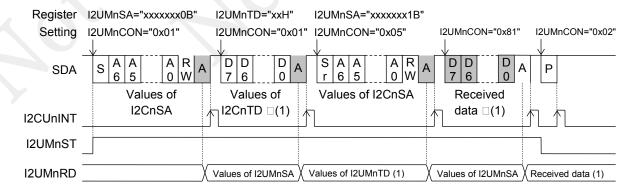

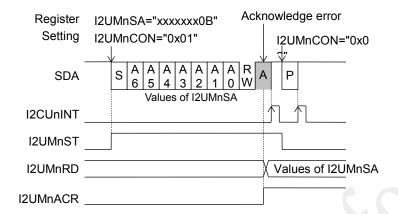

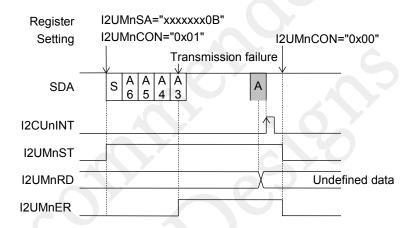

| 12.3.1           | Master Operation                                    |       |

| 12.3.1           | T                                                   |       |

| 12.3.1           |                                                     |       |

| 12.3.1           |                                                     |       |

| 12.3.1           |                                                     |       |

| 12.3.1           |                                                     |       |

| 12.3.1           |                                                     |       |

| 12.3.1           | $\varepsilon$                                       |       |

| 12.3.1           |                                                     |       |

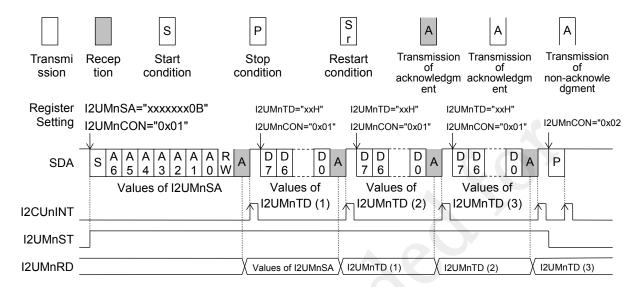

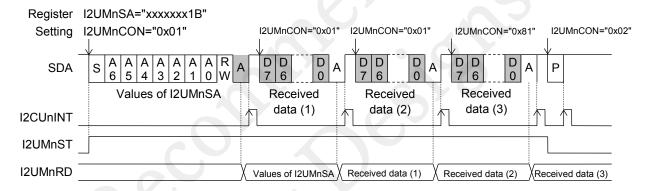

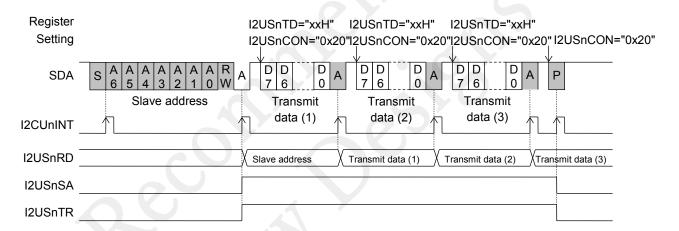

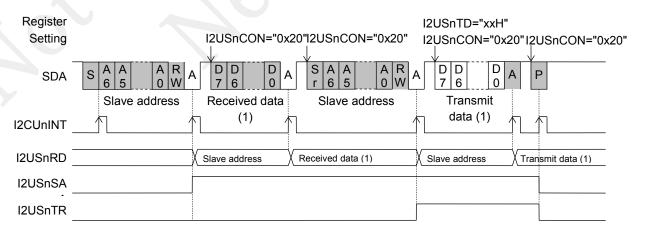

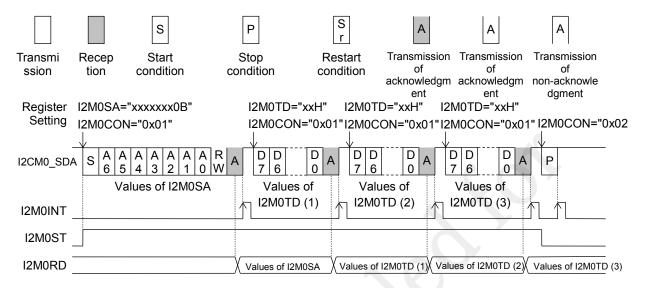

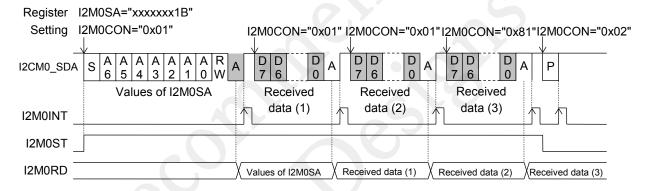

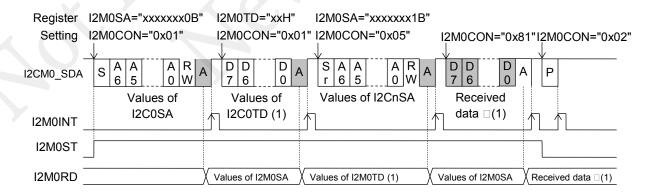

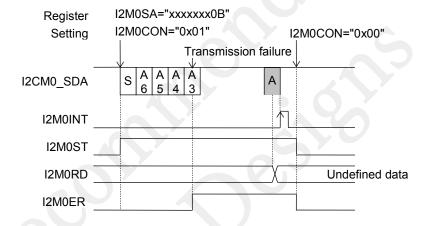

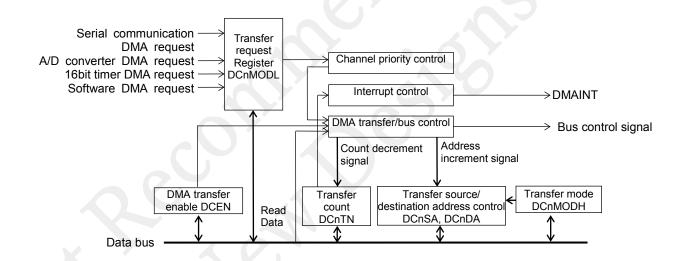

| 12.3.2<br>12.3.3 | Master Mode Communication Operation Timing          |       |

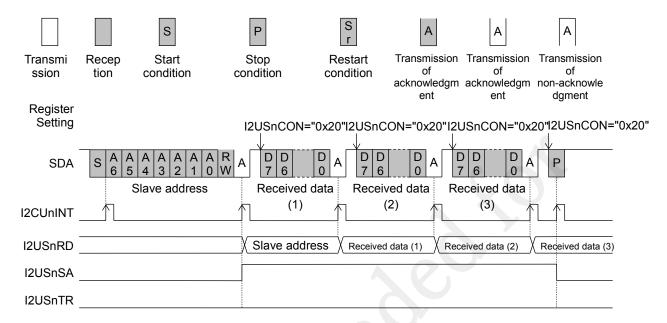

|                  | Slave Operation                                     |       |

| 12.3.3<br>12.3.3 | •                                                   |       |

| 12.3.3           |                                                     |       |

| 12.3.3           |                                                     |       |

| 12.3.3           |                                                     |       |

| 12.3.3           |                                                     |       |

| 12.3.3           |                                                     |       |

| 12.3.4           | Communication Operation Timing                      |       |

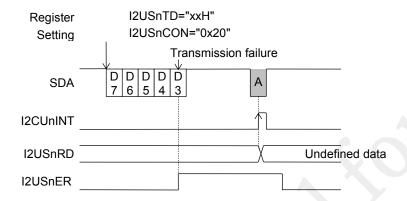

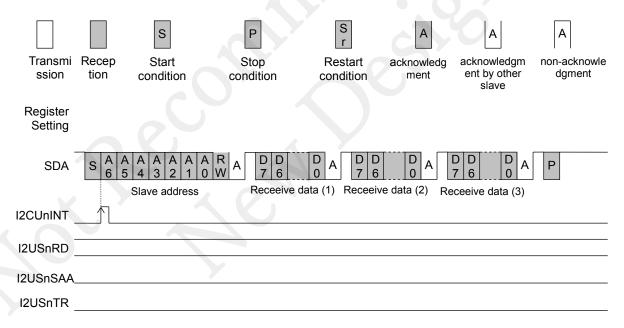

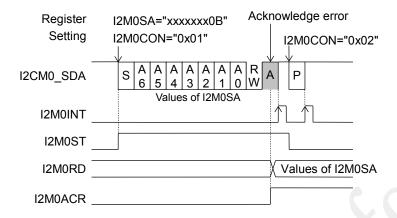

| 12.3.5           | Operation Waveforms                                 |       |

| 12.3.6           | Pin Settings                                        |       |

|                  |                                                     |       |

| hapter 13        |                                                     |       |

| 13 12C M         | aster                                               | 13_1  |

|                  | eral Description                                    |       |

| 13.1.1           | Features                                            |       |

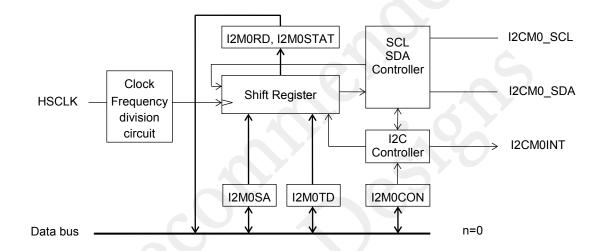

| 13.1.2           | Configuration                                       |       |

| 13.1.3           | List of Pins                                        |       |

|                  | cription of Registers                               |       |

| 13.2.1           | List of Registers                                   |       |

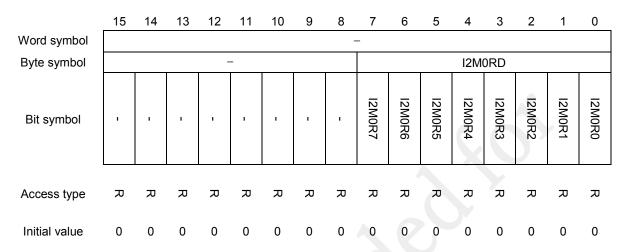

| 13.2.2           | I2C Master n Receive Register (I2MnRD.              |       |

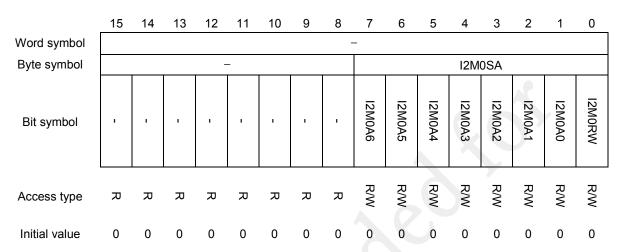

| 13.2.3           | I2C Master 0 Slave Address Register (I2M0SA)        |       |

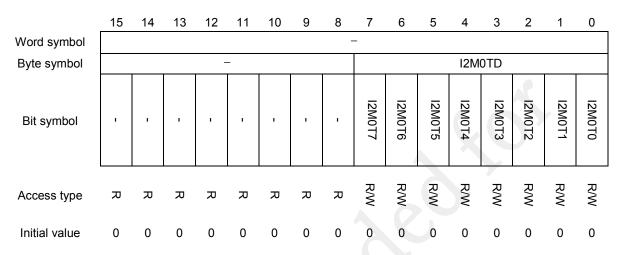

| 13.2.4           | I2C Master 0 Transmit Data Register (I2M0TD)        |       |

| 13.2.5           | I2C Master 0 Control Register (I2M0CON)             | 13-6  |

| 13.2.6           | I2C Master 0 Mode Register (I2M0MOD)                |       |

| 13.2.7           | I2C Master 0 Status Register (I2M0STAT)             | 13-10 |

| 13.3 Des         | cription of Operation                               | 13-11 |

| 13.3.1           | Master Operation                                    |       |

| 13.3.1           | .1 Communication Operation Mode                     | 13-11 |

| 13.3.1           | •                                                   |       |

| 13.3.1           |                                                     |       |

| 13.3.1           |                                                     |       |

| 13.3.1           |                                                     |       |

| 13.3.1           |                                                     |       |

| 13.3.1           |                                                     |       |

| 13.3.1           | 1                                                   |       |

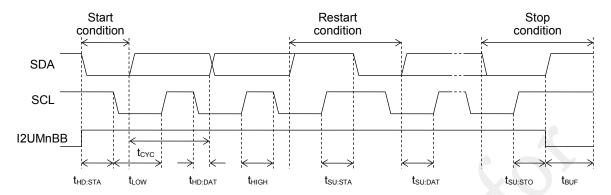

| 13 3 2           | Communication Operation Timing                      | 13-12 |

| 13.3.3<br>13.3.4 | Operation Waveforms Pin Settings                                           |         |

|------------------|----------------------------------------------------------------------------|---------|

|                  | Č                                                                          | 13-10   |

| Chapter 1        |                                                                            |         |

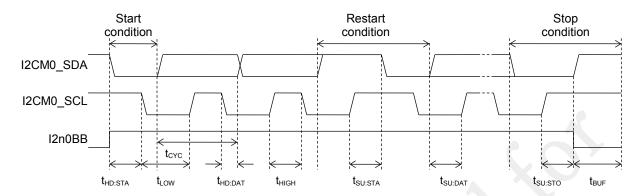

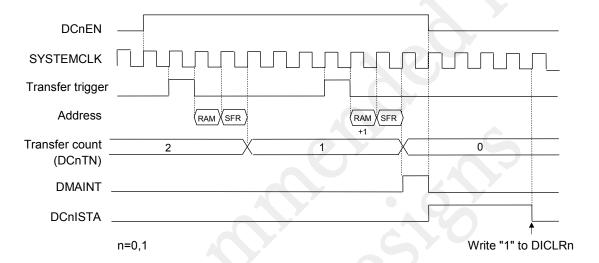

|                  | C (Direct Memory Access Controller)                                        |         |

|                  | neral Description                                                          |         |

| 14.1.1           | Features                                                                   |         |

| 14.1.2           | Configuration of Registers                                                 |         |

| 14.2 De          | scription of Registers                                                     |         |

| 14.2.1           | DMA Channel n Mode Register (DCnMOD: n = 0, 1)                             |         |

| 14.2.3           | DMA Channel n Transfer Count Register (DCnTN: n = 0, 1)                    |         |

| 14.2.4           | DMA Channel n Transfer Source Address Register (DCnSA: n = 0, 1)           |         |

| 14.2.5           | DMA Channel n Transfer Destination Address Register (DCnDA: n = 0, 1)      |         |

| 14.2.6           | DMA Enable Register (DCEN)                                                 |         |

| 14.2.7           | DMA Status Register (DSTAT)                                                |         |

| 14.2.8           | DMA Interrupt Status Clear Register (DICLR)                                | 14-11   |

| 14.3 De          | scription of Operation                                                     |         |

| 14.3.1           | DMA Operation Procedure                                                    |         |

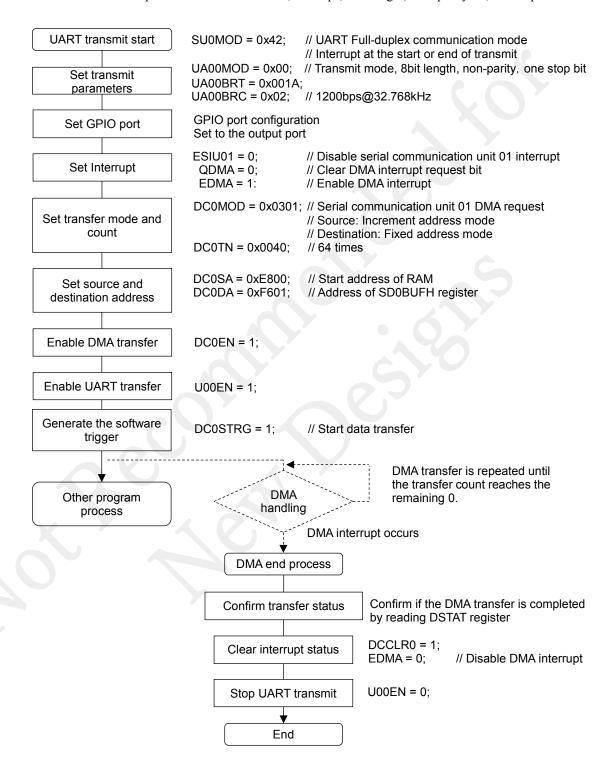

| 14.3.2           | UART Continuous Transmission                                               |         |

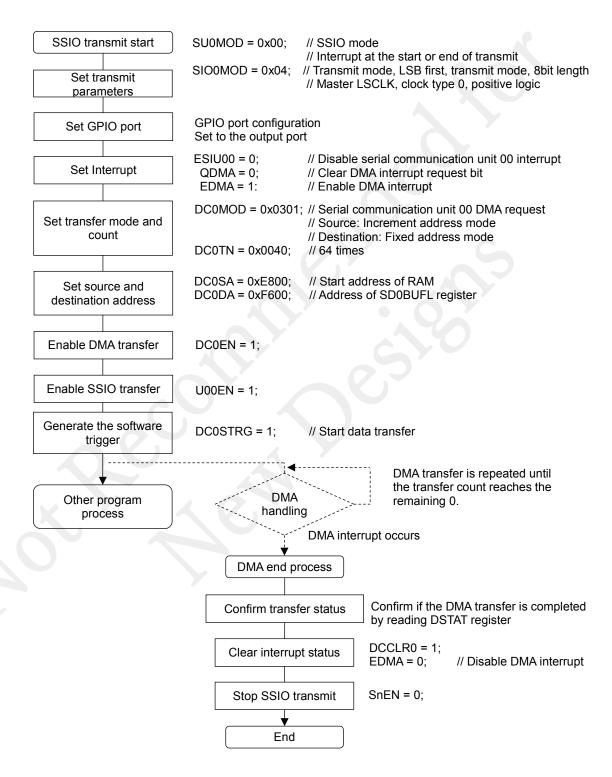

| 14.3.3           | SSIO Continuous Transmission                                               |         |

| 14.3.4           | DMA Transfer Target Block                                                  | 14-15   |

| Chapter 1        | 5                                                                          |         |

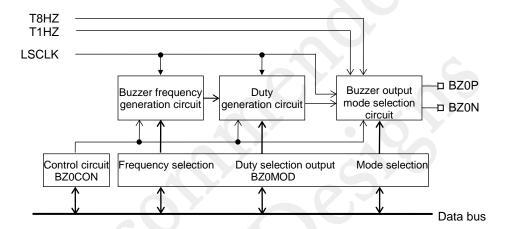

| 15. Buzzei       |                                                                            | 15-1    |

|                  | neral Description                                                          |         |

| 15.1.1           | Features                                                                   |         |

| 15.1.2           | Configuration                                                              |         |

| 15.1.3           | List of Pins                                                               | 15-2    |

| 15.2 De          | scription of Registers                                                     | 15-3    |

| 15.2.1           | List of Registers                                                          | 15-3    |

| 15.2.2           | Buzzer 0 Control Register (BZ0CON)                                         | 15-4    |

| 15.2.3           | Buzzer 0 Mode Register (BZ0MOD)                                            |         |

|                  | scription of Operation                                                     |         |

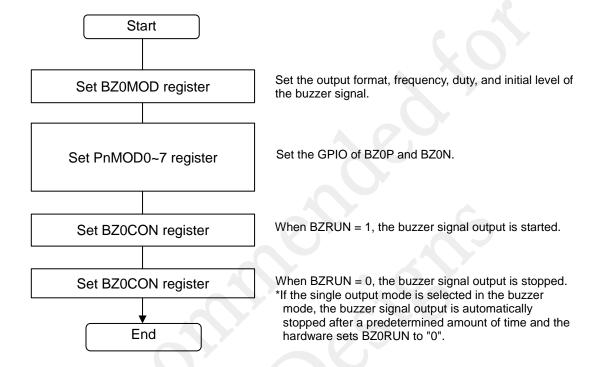

| 15.3.1           | Operation Flow                                                             |         |

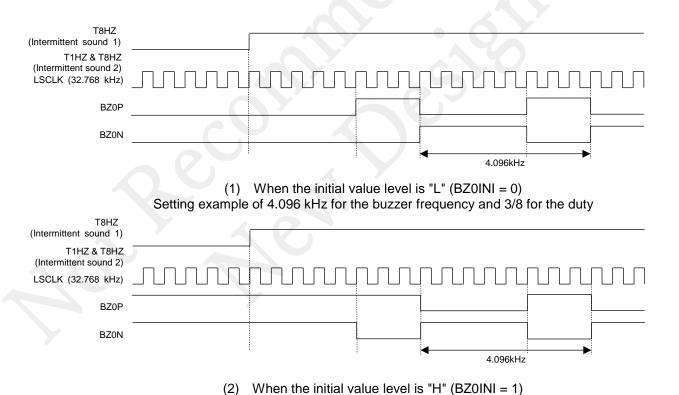

|                  | Buzzer Output Waveform                                                     |         |

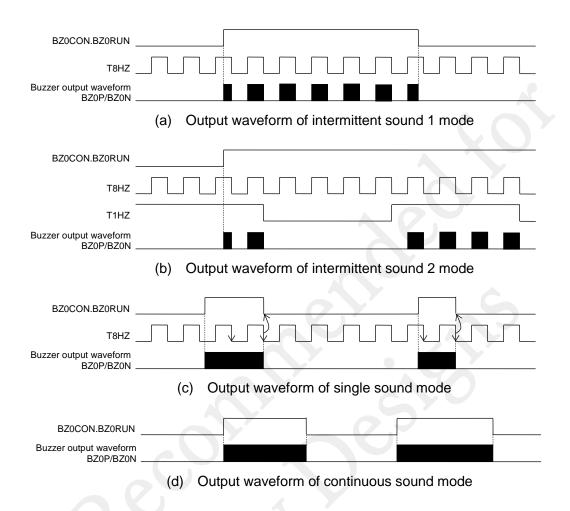

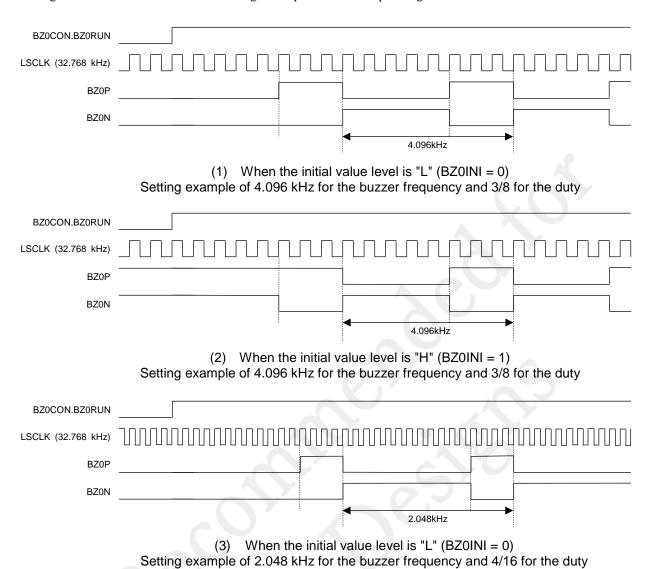

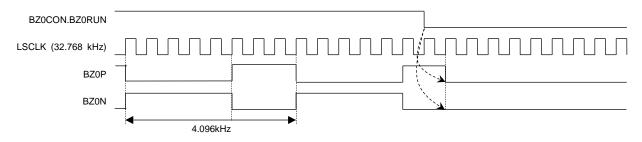

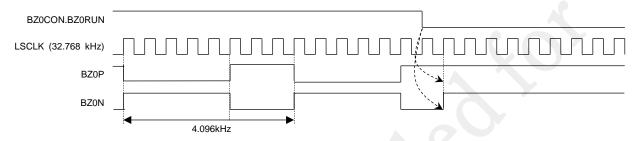

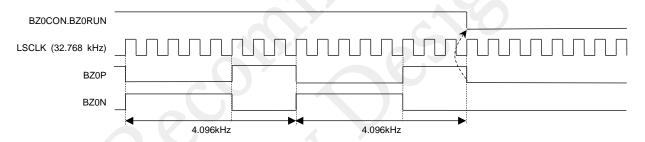

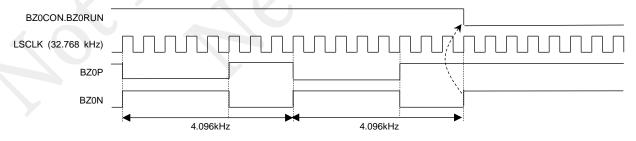

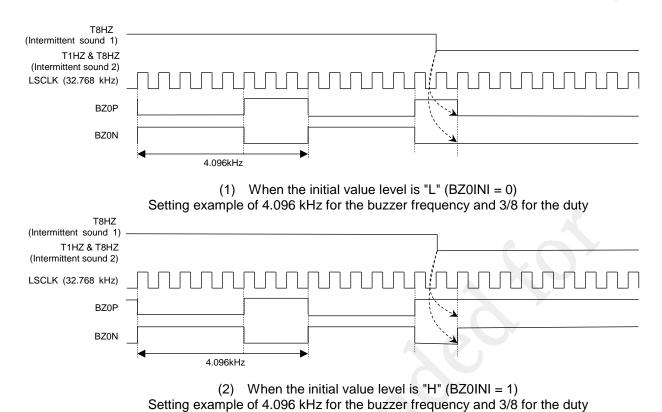

|                  | 2.1 Buzzer Output Waveform                                                 | 15-8    |

| 15.3.2<br>15.3.3 | Pin Settings                                                               |         |

| 13.3.3           | Till Settings                                                              | 13-12   |

| Chapter 1        | 5                                                                          |         |

| 16. Simp         | ified RTC                                                                  |         |

| Chapter 1        | 7                                                                          |         |

|                  | (General Purpose Input/Output)                                             |         |

|                  | neral Description                                                          |         |

| 17.1.1           | Features                                                                   |         |

| 17.1.2           | Configuration                                                              |         |

| 17.1.3           | List of Pins                                                               |         |

|                  | scription of Registers.                                                    |         |

| 17.2.1           | List of Registers                                                          |         |

| 17.2.2           | GPIO Interrupt Control Register 01 (EICON0)                                |         |

| 17.2.3<br>17.2.4 | Port n Mode Register 01 (PnMOD01) n: Port Number (0~3)                     |         |

| 17.2.4           | Port n Mode Register 45 (PnMOD45) n: Port Number $(0\sim3)$                |         |

| 17.2.5           | Port n Mode Register 67 (PnMOD67) n: Port Number $(0\sim2)$                |         |

| 1 / . 2.0        | TOTALL PARTOLE REGISTER OF (1 IIIVIODOF) II. I OIT INCHIDE ( $0^{\sim}2$ ) | 1 /-1 / |

| 17.2.7            | Port n Pulse Mode Register (PnPMD) n: Port Number (0~3)            | 17-20 |

|-------------------|--------------------------------------------------------------------|-------|

| 17.3 De           | scription of Operation                                             | 17-21 |

| 17.3.1            | Input Function                                                     |       |

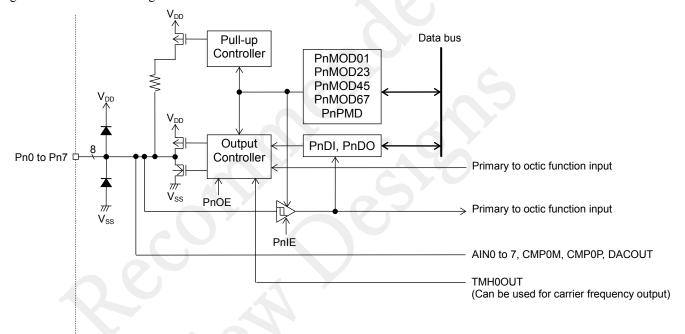

| 17.3.2            | Output Function                                                    |       |

| 17.3.3            | Primary Function Other Than Input/Output Function                  | 17-21 |

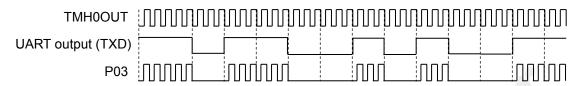

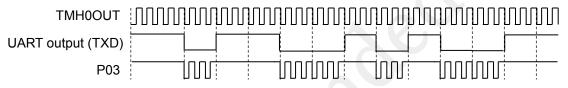

| 17.3.4            | Shared Function (Secondary to Octic Function)                      |       |

| 17.3.5            | Carrier Frequency Output Function                                  |       |

| 17.3.6            | GPIO Test Function                                                 |       |

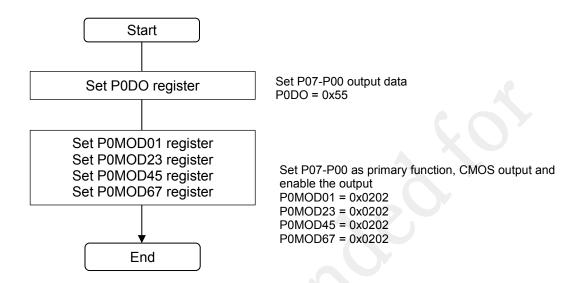

| 17.3.7            | Setting Example of Port                                            |       |

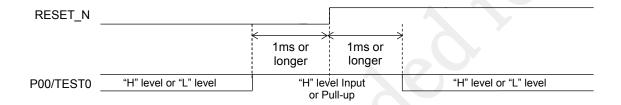

| 17.3.8            | Notes for using the P00/TEST0 pin                                  |       |

| 17.3.             |                                                                    |       |

| 17.3.             |                                                                    |       |

| Chapter 1         | 8                                                                  |       |

| 18. Exter         | nal Interrupt Control Circuit                                      | 18-1  |

| 18.1 Ge           | neral Description                                                  | 18-1  |

| 18.1.1            | Features                                                           | 18-1  |

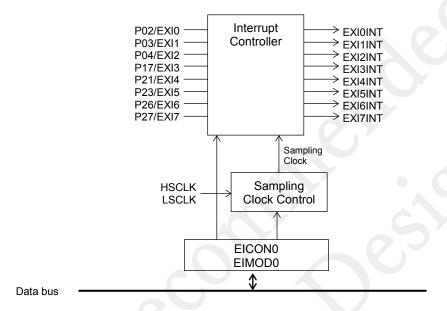

| 18.1.2            | Configuration                                                      | 18-1  |

| 18.1.3            | List of Pins                                                       | 18-2  |

| 18.2 De           | scription of Registers                                             | 18-3  |

| 18.2.1            | List of Registers                                                  | 18-3  |

| 18.2.2            | External Interrupt Control Register 01 (EICON0)                    | 18-4  |

| 18.2.3            | External Interrupt Mode Register 0 (EIMOD0)                        |       |

| 18.3 De           | scription of Operation                                             | 18-7  |

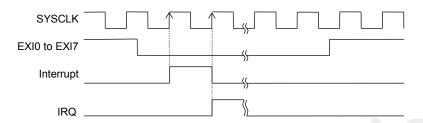

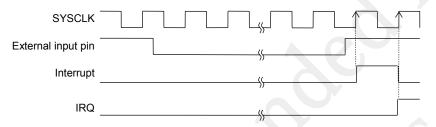

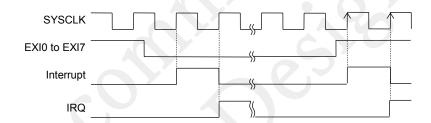

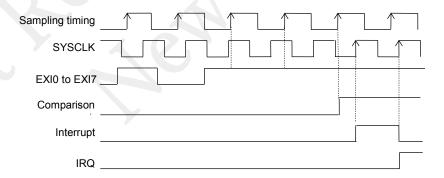

| 18.3.1            | Interrupt Request Timing                                           | 18-7  |

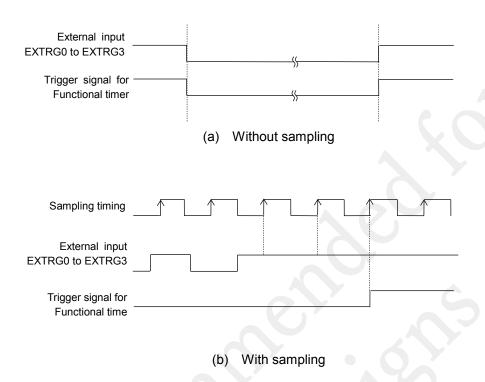

| 18.3.2            | External Trigger Signal to Functional Timer                        | 18-8  |

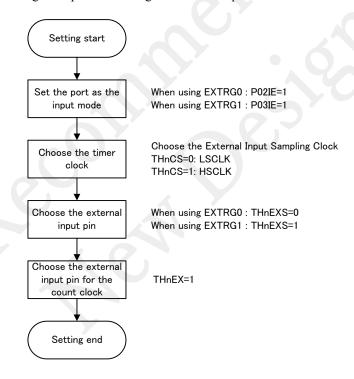

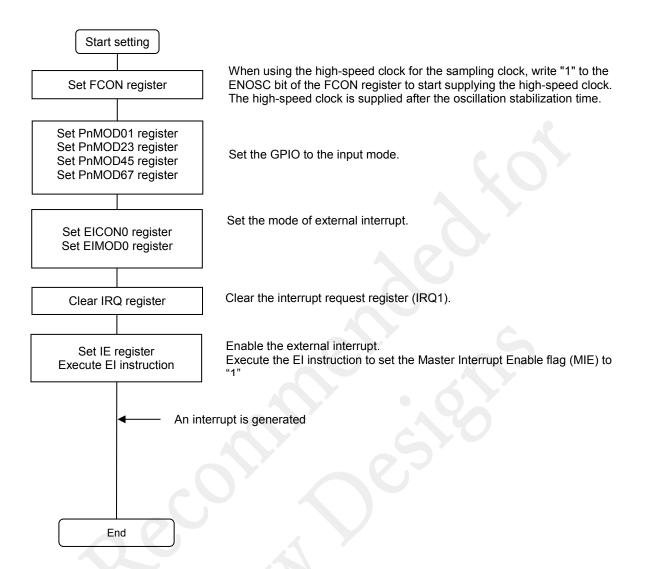

| 18.3.3            | External Interrupt Setting Flow                                    | 18-9  |

| Chapter 1         | 9                                                                  |       |

| 19. CRC           |                                                                    |       |

| 19.1 Ge           | (Cycle Redundancy Check) Generatorneral Description                | 19-1  |

| 19.1.1            | Features                                                           |       |

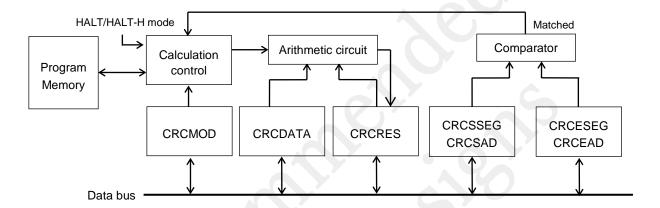

| 19.1.2            | Configuration                                                      |       |

|                   | scription of Registers                                             |       |

| 19.2.1            | List of Registers                                                  |       |

| 19.2.2            | Automatic CRC Calculation Start Address Setting Register (CRCSAD)  |       |

| 19.2.3            | Automatic CRC Calculation End Address Setting Register (CRCEAD)    |       |

| 19.2.4            | Automatic CRC Calculation Start Segment Setting Register (CRCSSEG) |       |

| 19.2.5            | Automatic CRC Calculation End Segment Setting Register (CRCESEG)   |       |

| 19.2.6            | CRC Data Register (CRCDATA)                                        |       |

| 19.2.7            | CRC Calculation Result Register (CRCRES)                           |       |

| 19.2.8            | Automatic CRC Mode Register (CRCMOD)                               |       |

|                   | scription of Operation                                             |       |

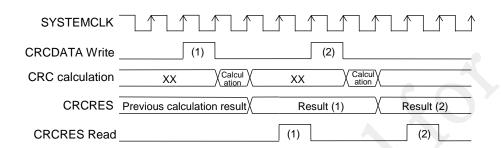

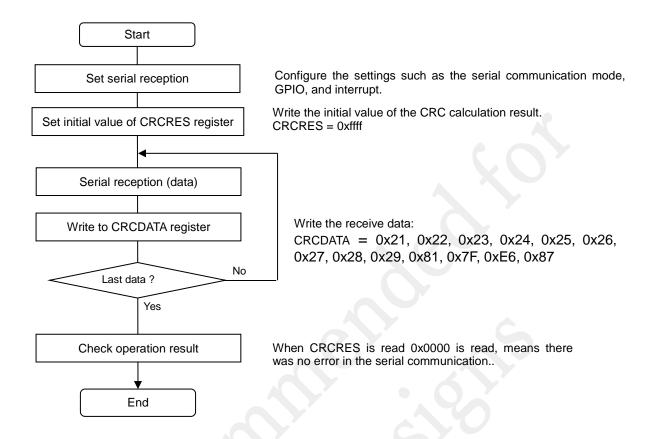

| 19.3.1            | CRC Calculation Mode                                               |       |

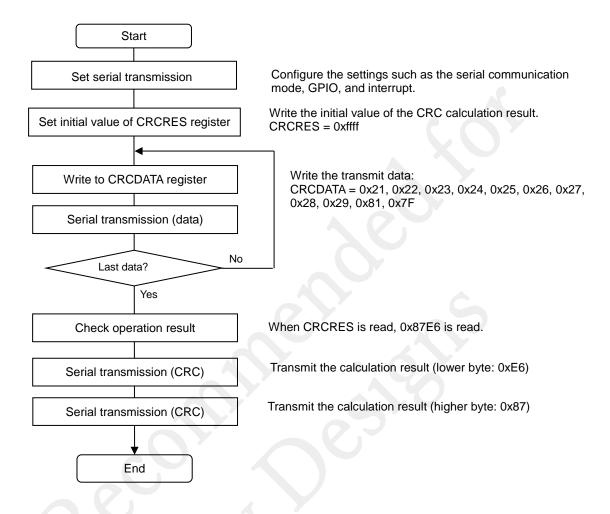

| 19.3.2            | Example of Use of CRC Calculation Mode                             |       |

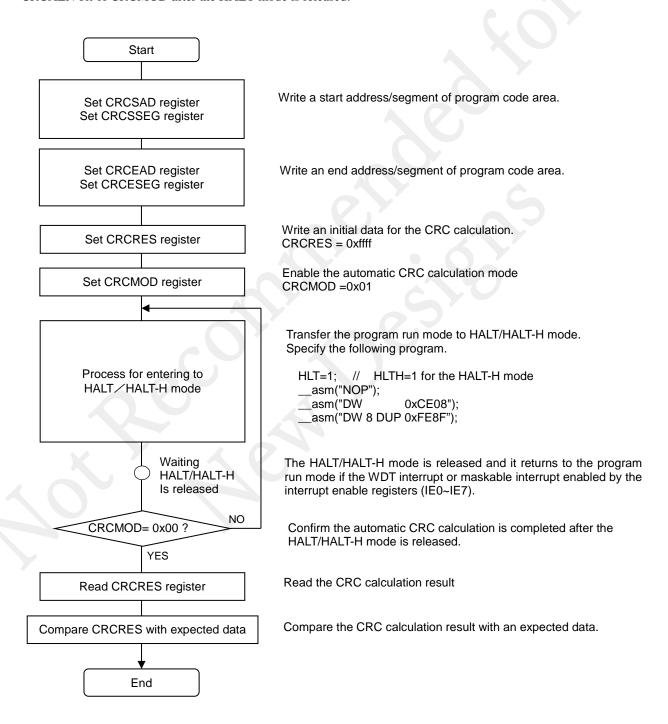

| 19.3.3            | Automatic CRC Calculation Mode                                     |       |

| Chapter 2         | 0                                                                  |       |

|                   | og Comparator                                                      | 20-1  |

|                   | neral Description                                                  |       |

| 20.1 Ge           | Features                                                           |       |

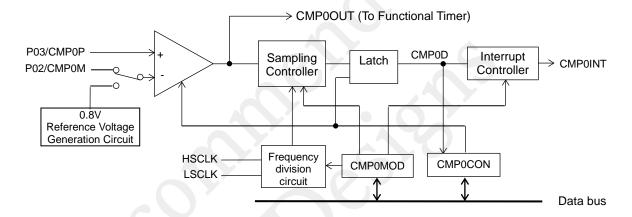

| 20.1.1            | Configuration                                                      |       |

| 20.1.2            | List of Pins                                                       |       |

|                   | scription of Registers                                             |       |

| 20.2 De<br>20.2.1 |                                                                    |       |

| 20.2.1            | List of Registers                                                  |       |

|                   | Comparator 0 Control Register (CMP0CON)                            |       |

| 20.2.3            | Comparator 0 Mode Register (CMP0MOD)                               |       |

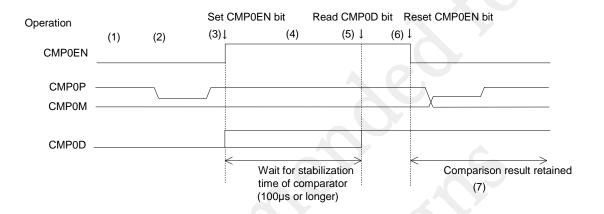

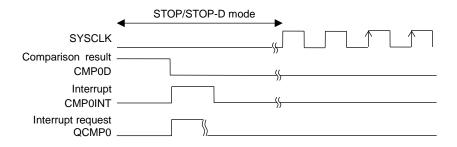

| 20.3 De<br>20.3.1<br>20.3.2 | scription of Operation Operation of Analog Comparator                      | 20-6  |

|-----------------------------|----------------------------------------------------------------------------|-------|

| Chapter 2                   | 1                                                                          |       |

| 21 D/A                      | Converter                                                                  | 21_1  |

|                             | neral Description                                                          |       |

| 21.1.1                      | Features                                                                   |       |

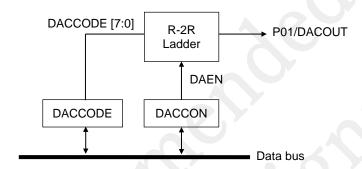

| 21.1.2                      | Configuration                                                              |       |

| 21.1.3                      | List of Pins                                                               |       |

| 21.2 De                     | scription of Registers                                                     |       |

| 21.2.1                      | List of Registers                                                          | 21-2  |

| 21.2.2                      | D/A Converter Enable Register (DACEN)                                      |       |

| 21.2.3                      | D/A Converter Code Register (DACCODE)                                      |       |

|                             | scription of Operation                                                     |       |

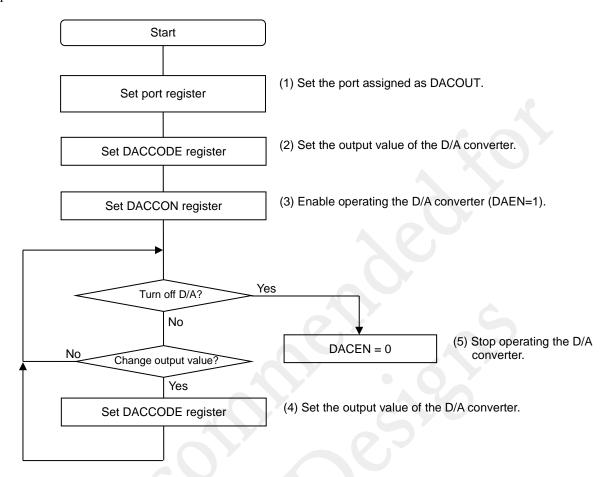

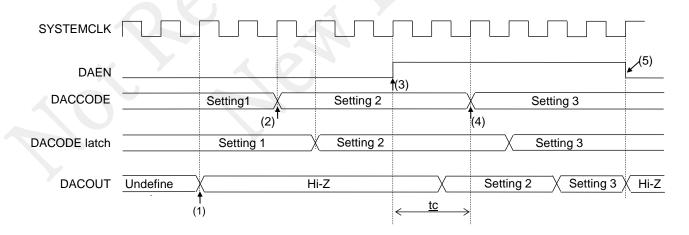

| 21.3.1                      | Operation of D/A Converter                                                 | 21-5  |

| Chapter 2                   | 2                                                                          |       |

| 22 Volta                    | ge Level Supervisor (VLS)                                                  | 22_1  |

|                             | neral Description                                                          |       |

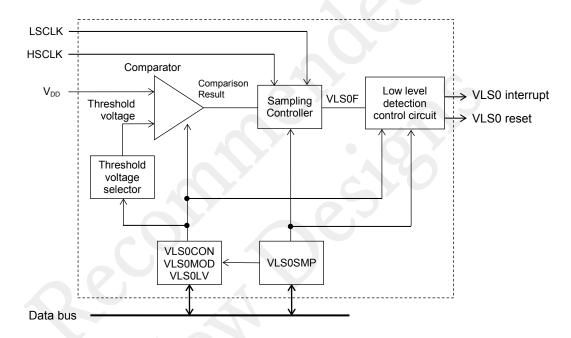

| 22.1.1                      | Features                                                                   |       |

| 22.1.2                      | Configuration                                                              |       |

|                             | scription of Registers                                                     |       |

| 22.2.1                      | List of Registers                                                          |       |

| 22.2.2                      | Voltage Level Supervisor Control Register (VLS0CON)                        |       |

| 22.2.3                      | Voltage Level Supervisor Mode Register (VLS0MOD)                           |       |

| 22.2.4                      | Voltage Level Supervisor 0 Level Register (VLS0LV)                         |       |

| 22.2.5                      | Voltage Level Supervisor 0 Sampling Register (VLS0SMP)                     |       |

|                             | scription of Operation                                                     |       |

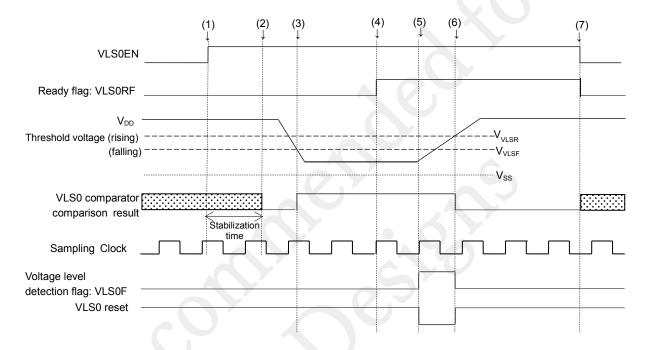

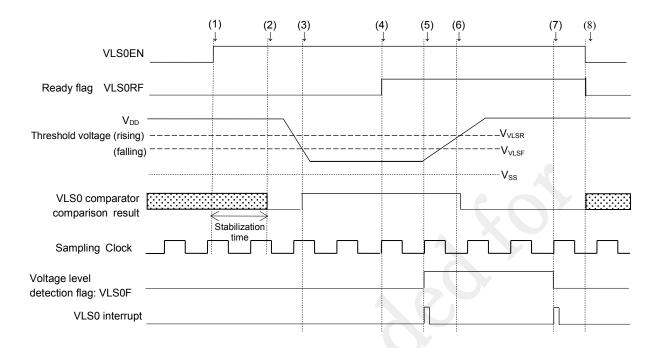

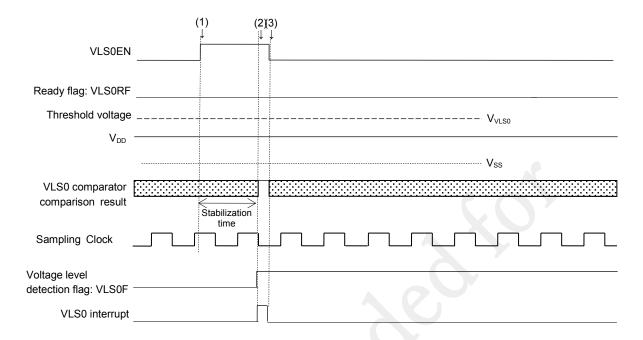

| 22.3.1                      | Supervisor Mode                                                            |       |

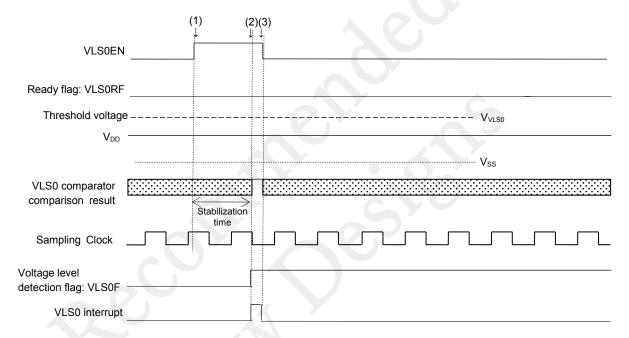

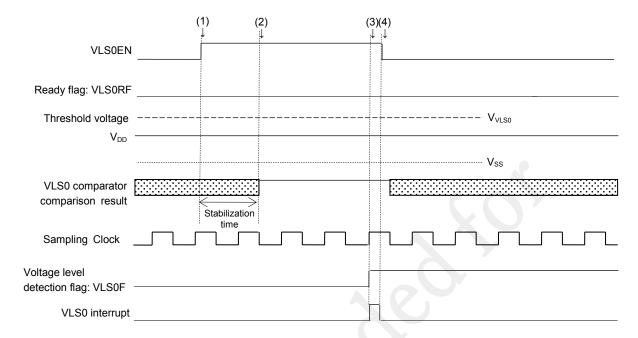

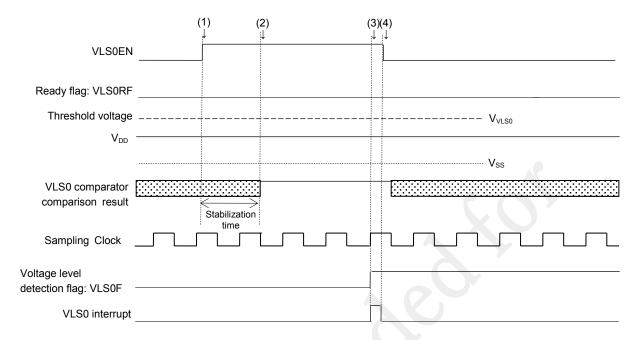

| 22.3.2                      | Single Mode                                                                | 22-14 |

| Chapter 2                   | 3                                                                          |       |

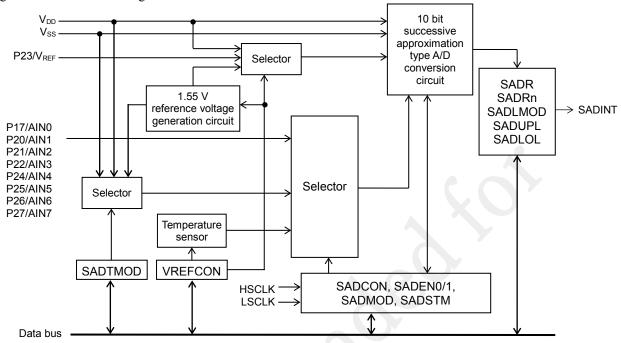

|                             | essive Approximation Type A/D Converter                                    | 22.1  |

|                             | neral Description                                                          |       |

| 23.1 06                     | Features                                                                   |       |

| 23.1.2                      | Configuration                                                              |       |

| 23.1.3                      | List of Pins                                                               |       |

|                             | scription of Operation                                                     |       |

| 23.2.1                      | List of Registers                                                          |       |

| 23.2.2                      | SA-ADC Result Register n (SADRn: n=0 to 7, 16)                             |       |

| 23.2.3                      | SA-ADC Result Register (SADR)                                              | 23-7  |

| 23.2.4                      | SA-ADC Upper/Lower Limit Status Register 0 (SADULS0)                       |       |

| 23.2.5                      | SA-ADC Upper/Lower Limit Status Register 1 (SADULS1)                       |       |

| 23.2.6                      | SA-ADC Mode Register (SADMOD)                                              |       |

| 23.2.7                      | SA-ADC Control Register (SADCON)                                           |       |

| 23.2.8                      | SA-ADC Enable Register 0 (SADEN0)                                          |       |

| 23.2.9                      | SA-ADC Enable Register 1 (SADEN1)                                          |       |

| 23.2.10                     |                                                                            |       |

| 23.2.11                     |                                                                            |       |

| 23.2.12                     |                                                                            |       |

| 23.2.13                     | SA-ADC Lower Limit Setting Register (SADLOL)                               |       |

|                             | SA-ADC Interrupt Mode Register (SADIMOD)                                   |       |

|                             | SA-ADC Interrupt Wode Register (SADIWOD)  SA-ADC Trigger Register (SADTRG) |       |

|                             | SA-ADC trigger Register (SADTRO)                                           |       |

|                             | scription of Operation                                                     |       |

|                             | ±                                                                          |       |

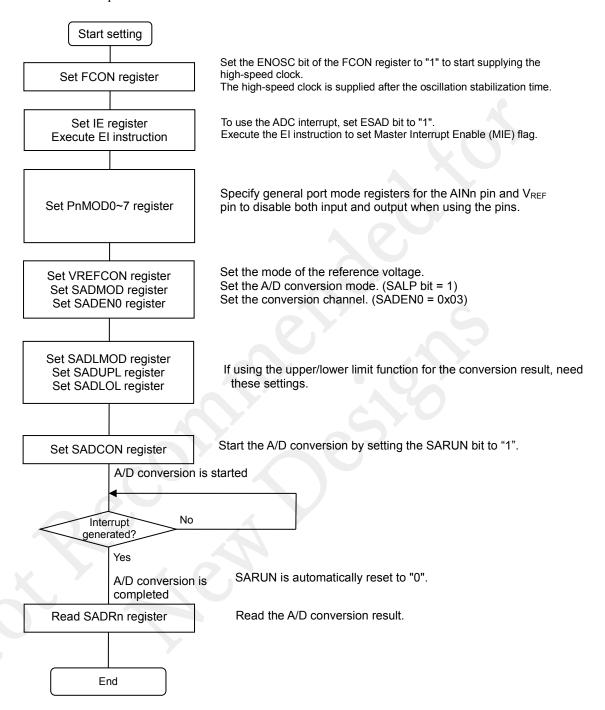

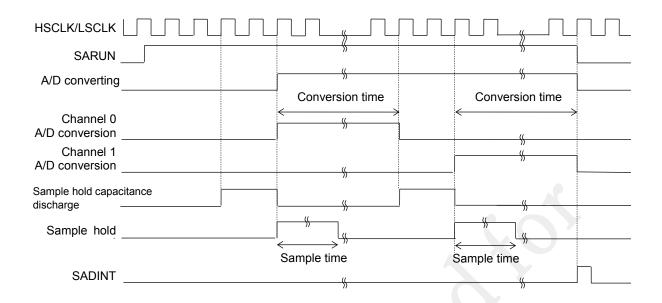

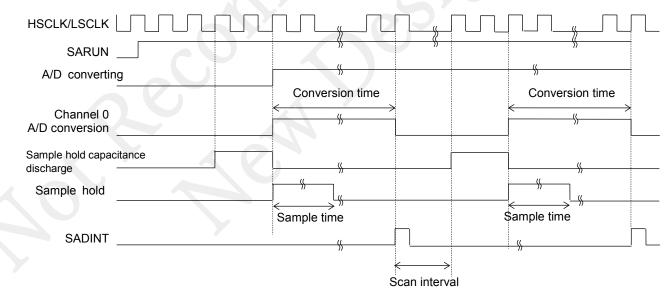

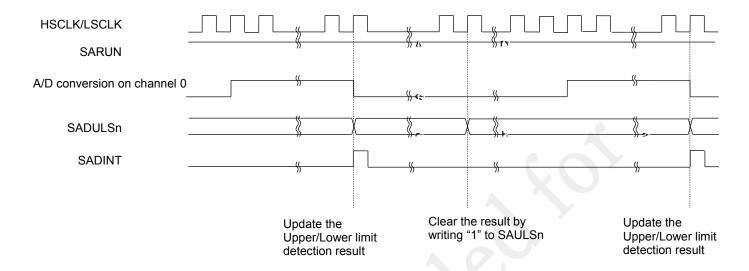

| 23.3.1<br>23.3.2 | Operation of Successive Approximation Type A/D Converter |       |

|------------------|----------------------------------------------------------|-------|

| Chapter 2        | 24                                                       |       |

| 24. Regu         | ılator                                                   | 24-1  |

| _                | eneral Description                                       |       |

| 24.1.1           | Features                                                 |       |

| 24.1.2           | Configuration                                            | 24-1  |

| 24.2 Ge          | eneral Description                                       | 24-2  |

| 24.2.1           | Reference Voltage Output                                 | 24-2  |

| Chapter 2        | 25                                                       | 70'   |

| 25. Flash        | Memory                                                   | 25-1  |

|                  | eneral Description                                       |       |

| 25.1.1           | Features                                                 |       |

|                  | escription of Registers                                  |       |

| 25.2.1           | List of Registers                                        |       |

| 25.2.2           | Flash Address Register (FLASHA)                          |       |

| 25.2.3           | Flash Segment Register (FLASHSEG)                        |       |

| 25.2.4           | Flash Data Register 0 (FLASHD0)                          |       |

| 25.2.5           | Flash Data Register 1 (FLASHD1)                          |       |

| 25.2.6<br>25.2.7 | Flash Control Register (FLASHCON)                        |       |

| 25.2.7           | Flash Acceptor (FLASHACP)                                |       |

| 25.2.8           | Flash Status Register (FLASHSTA)                         | 25-10 |

|                  | lf-programming                                           |       |

| 25.3.1           | Notes on debugs for self-programming codes               |       |

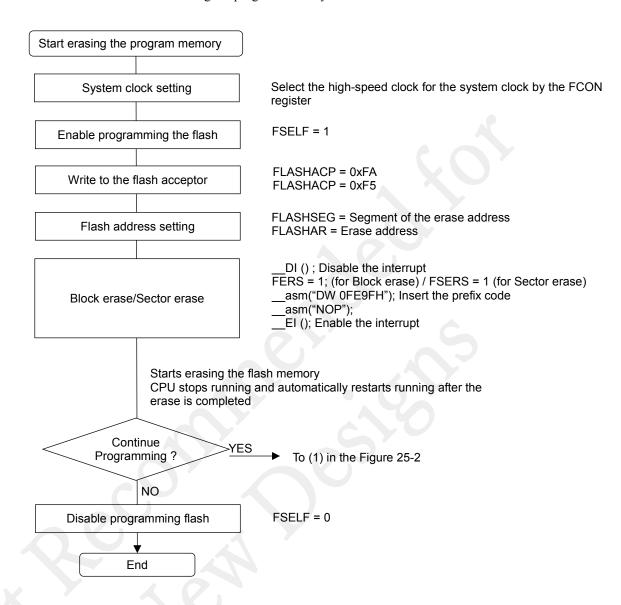

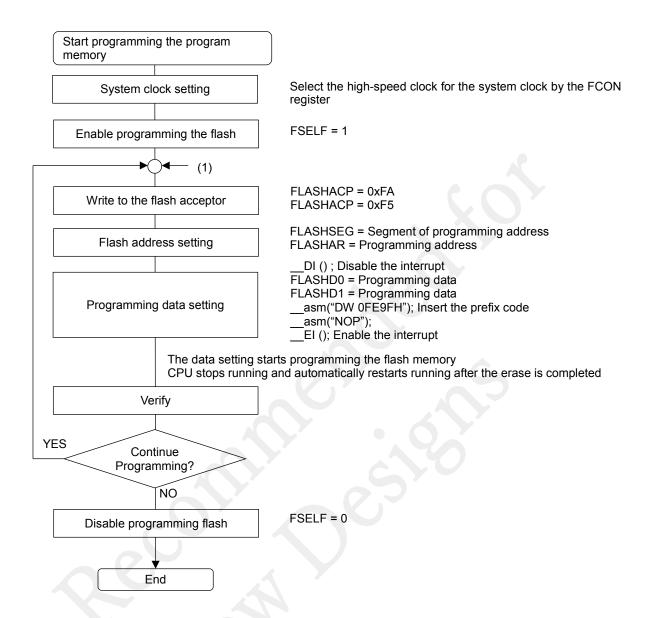

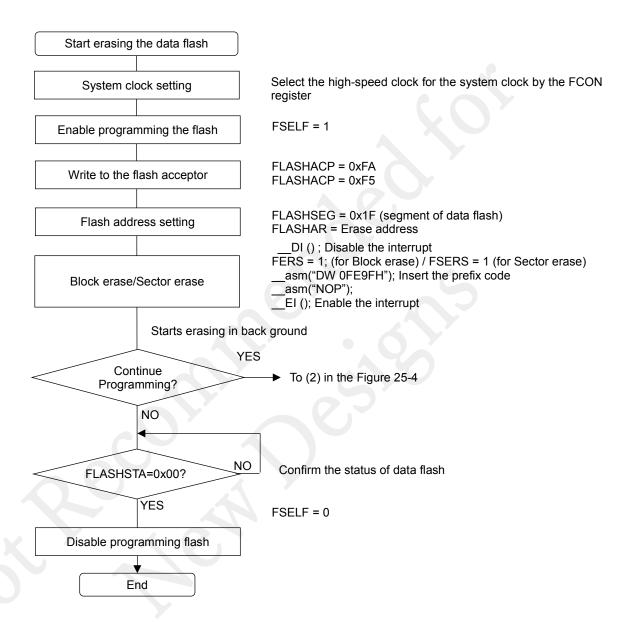

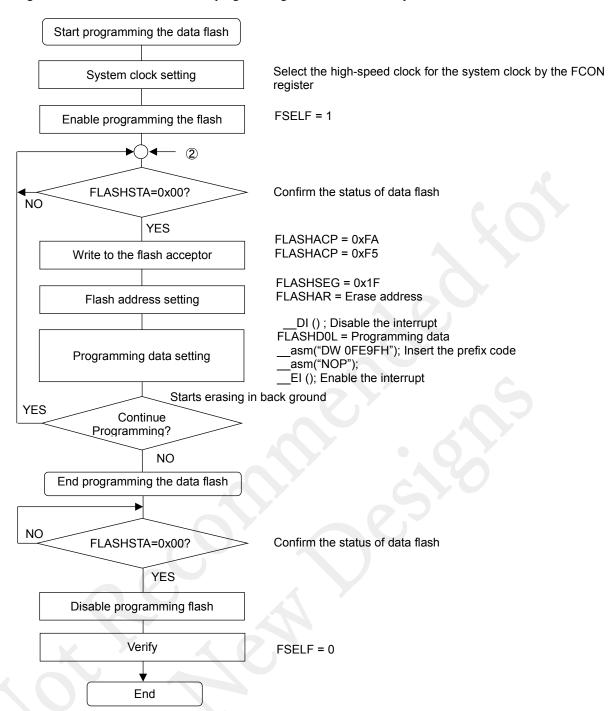

| 25.3.2           | Programming the program memory                           | 25-12 |

| 25.3.3           | Programming thd data flash memory                        |       |

| 25.3.4           | Notes in Use of the self-programming                     |       |

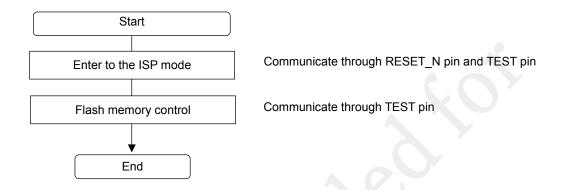

| 25.4 IS          | P Function                                               | 25-17 |

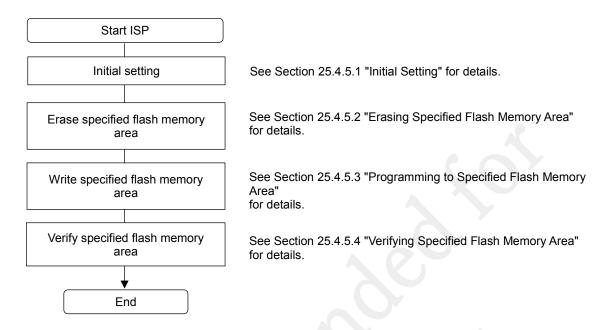

| 25.4.1           | Programming procedure                                    | 25-17 |

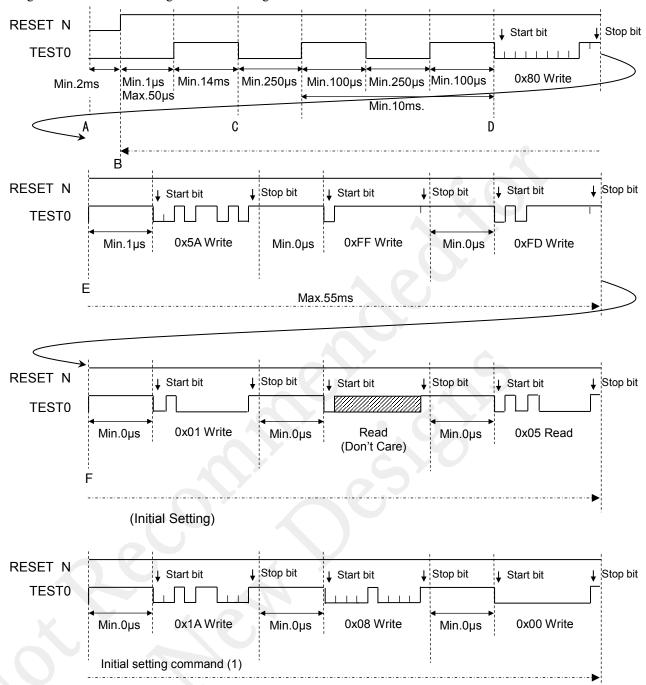

| 25.4.2           | Communication method                                     |       |

| 25.4.3           | Communication command                                    |       |

| 25.4.4           | ISP mode transition                                      |       |

| 25.4.5           | Flash Memory Control                                     |       |

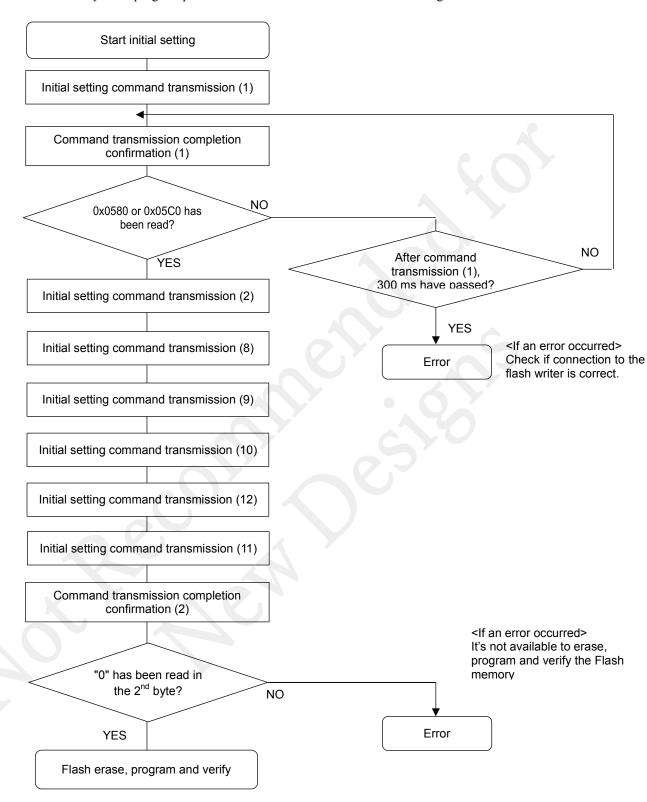

|                  | 5.1 Initazation                                          |       |

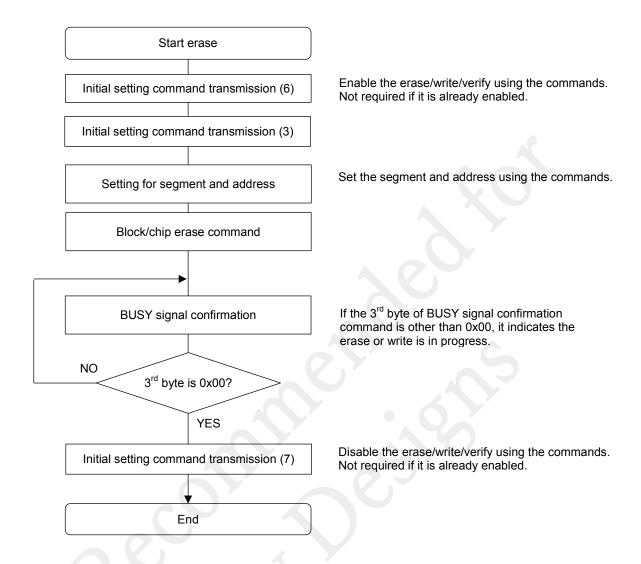

| 25.4.<br>25.4.   |                                                          |       |

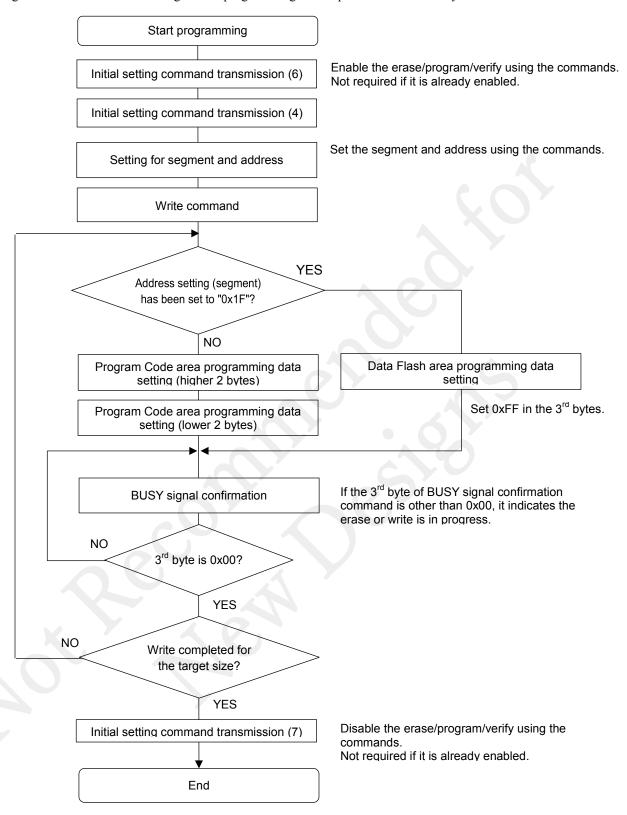

| 25.4.<br>25.4.   |                                                          |       |

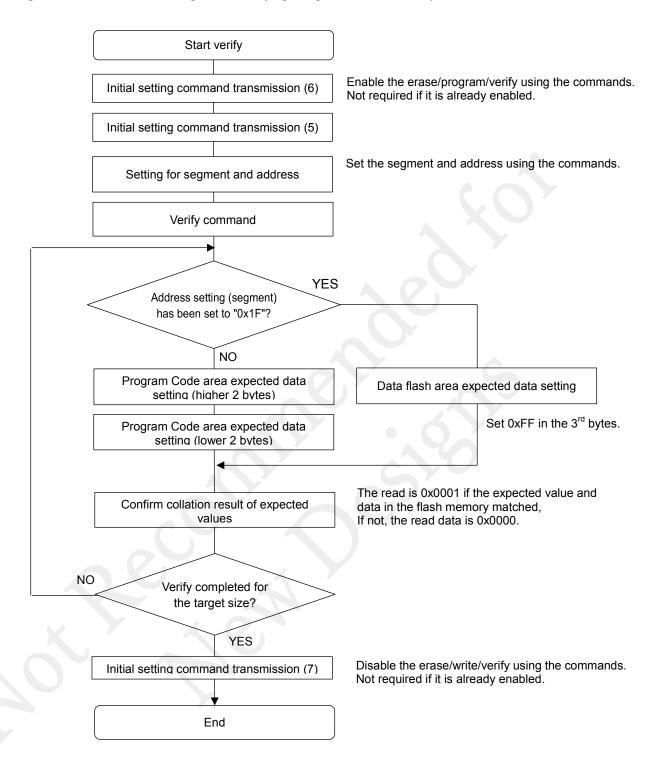

| 23.1.            | 3.1 Verification                                         |       |

| Chapter 2        | 26                                                       |       |

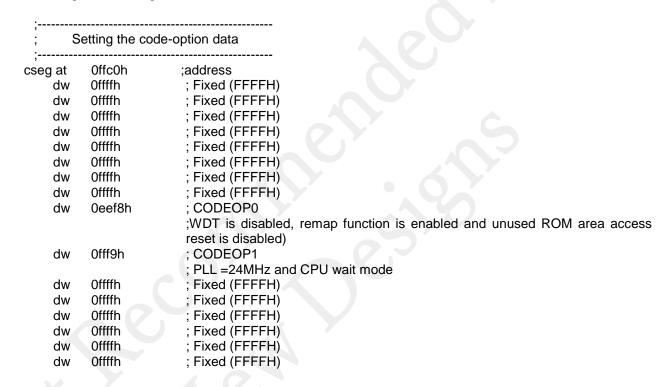

| 26. Code         | Option                                                   | 26-1  |

|                  | eneral Description                                       |       |

| 26.1.1           | Features                                                 |       |

|                  | escription of Code Option                                |       |

| 26.2.1           | Code Options 0 (CODEOP0)                                 |       |

| 26.2.2           | Code Options 1 (CODEOP1)                                 |       |

| 26.3 Ho          | ow to configure the Code Option data                     | 26-5  |

| Chapter 2        | 27                                                       |       |

| 27 1.0           | D driver                                                 |       |

Chapter 28

ML62Q1200A Group User's Manual Contents

|                          | p debug function                                            |       |

|--------------------------|-------------------------------------------------------------|-------|

| 28.1 General Description |                                                             |       |

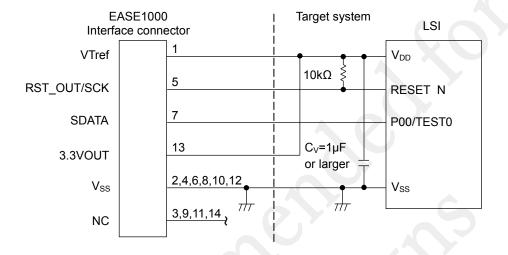

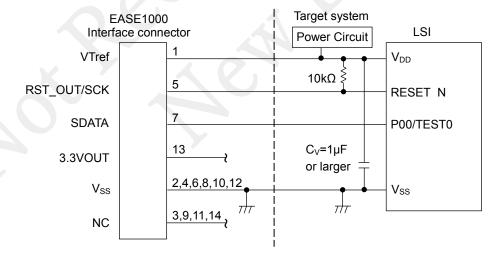

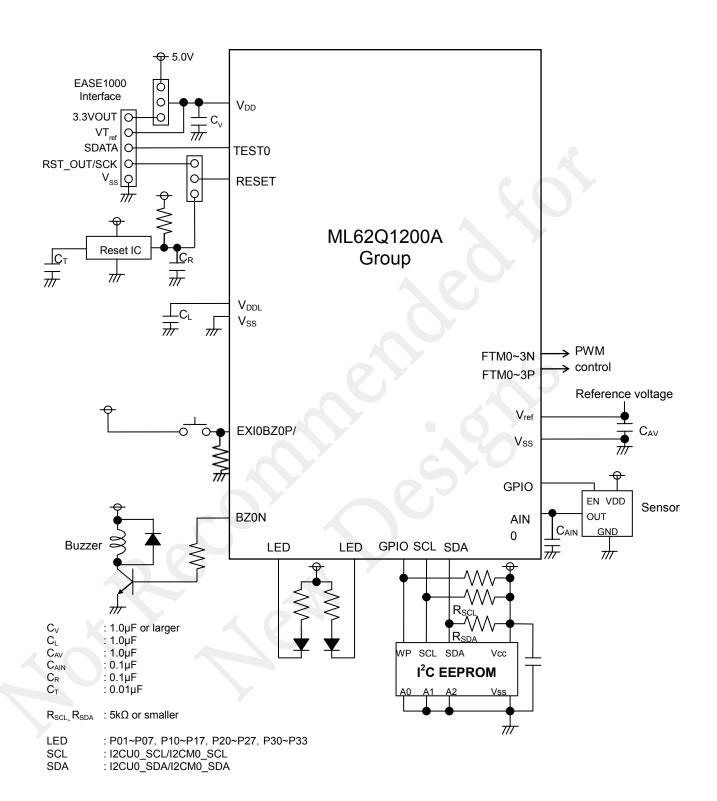

|                          | nnection with the On-chip Debug Emulator EASE1000           |       |

|                          | tes on Debug with EASE1000                                  |       |

|                          | erview of On-Chip Debug Function                            |       |

| 28.4.1                   | Peripheral Operation Continuation/Stop Control during Break | 28-3  |

| Chapter 2                | 9                                                           |       |

|                          | Function                                                    | 29-1  |

|                          | neral Description                                           |       |

| 29.1.1                   | Features                                                    |       |

| 29.2 De                  | scription of Registers                                      |       |

| 29.2.1                   | List of Registers                                           |       |

| 29.2.2                   | RAM Guard Setting Register (RAMGD)                          |       |

| 29.2.3                   | SFR Guard Setting Register 0 (SFRGD0)                       |       |

| 29.2.4                   | SFR Guard Setting Register 1 (SFRGD1)                       |       |

| 29.2.5                   | RAM Parity Setting Register (RASFMOD)                       |       |

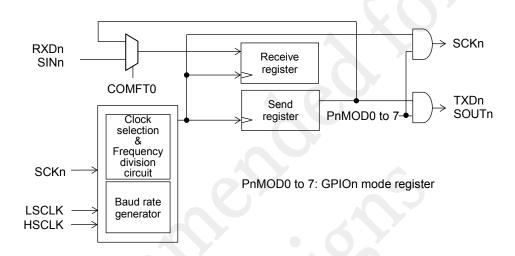

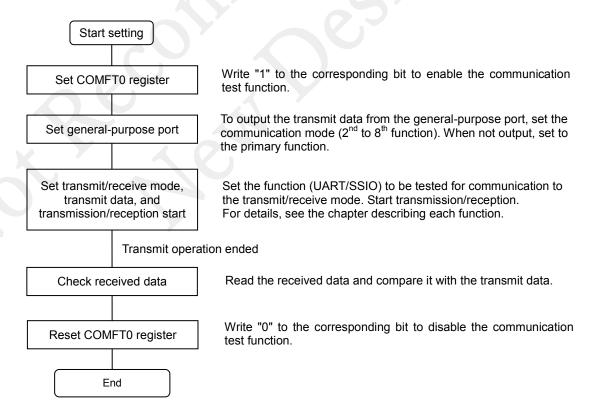

| 29.2.6                   | Communication Test Setting Register (COMFT0)                |       |

| 29.3 De                  | scription of Operation                                      |       |

| 29.3.1                   | Communication Function Self-Test                            | 29-8  |

| 29.3.2                   | Unused ROM Area Access Reset Function                       | 29-9  |

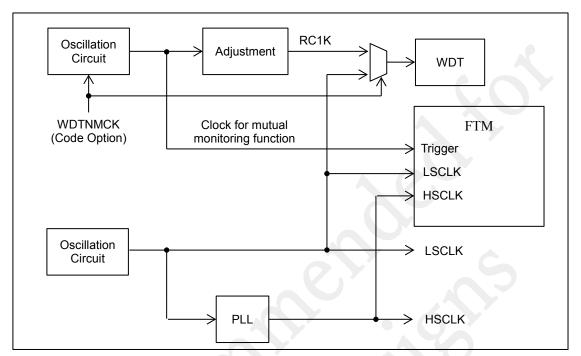

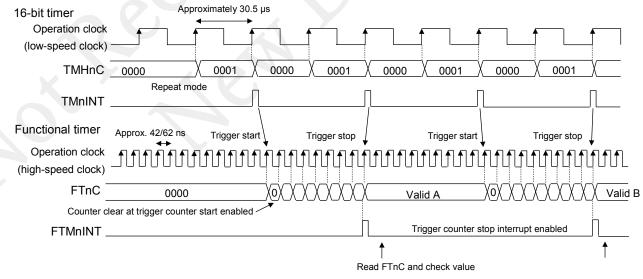

| 29.3.3                   | Clock Mutual Monitoring Function                            | 29-10 |

| 29.3.4                   | CRC Calculation                                             | 29-12 |

| 29.3.5                   | WDT Counter Read                                            | 29-12 |

| 29.3.6                   | Port Output Level Test                                      | 29-12 |

| 29.3.7                   | Successive Approximation Type A/D Converter Test            | 29-12 |

| Appendix                 | es                                                          |       |

|                          |                                                             |       |

| Appendix                 | A Register List                                             | A-1   |

#### **Revision History**

Appendix A Appendix B

Appendix C

Appendix D Appendix E

| Revision History | · | R-1 |

|------------------|---|-----|

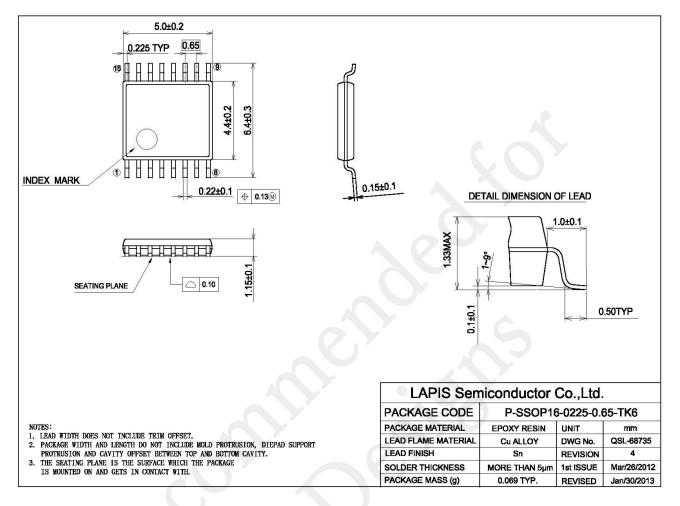

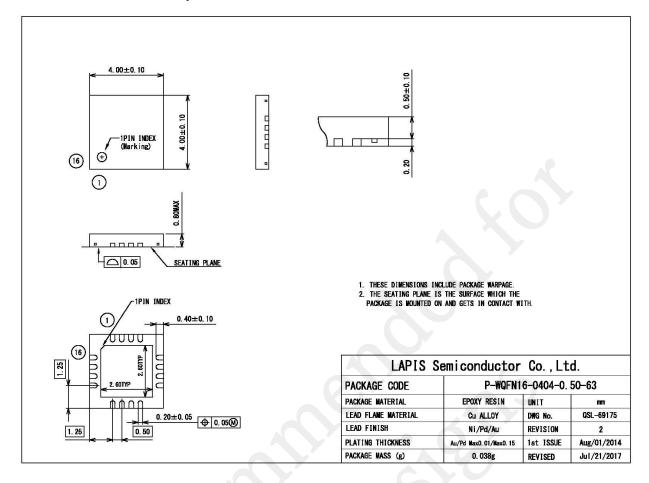

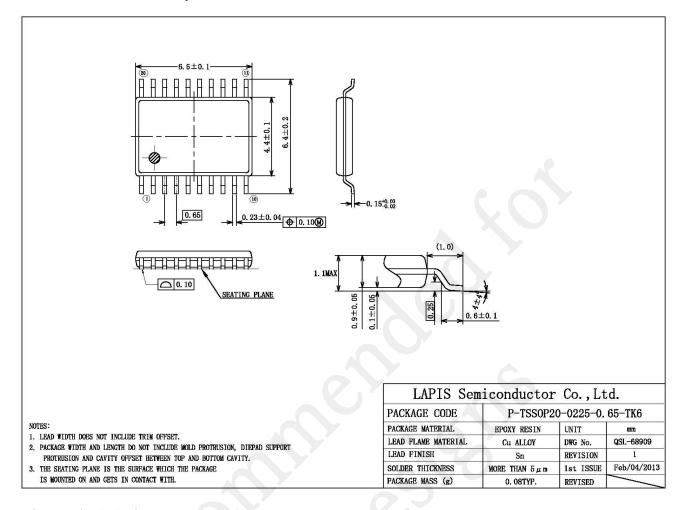

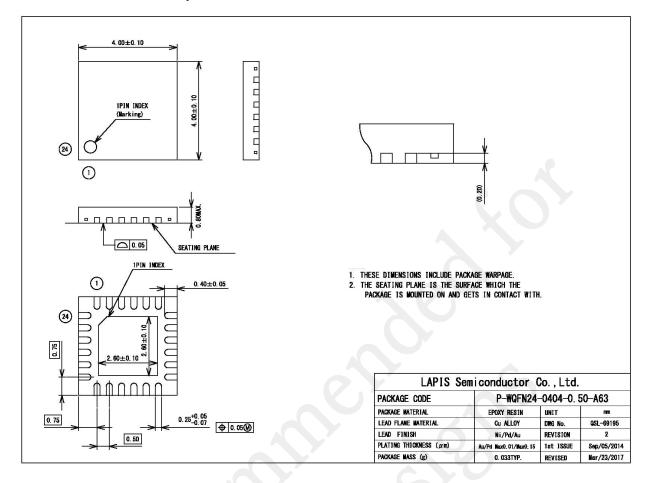

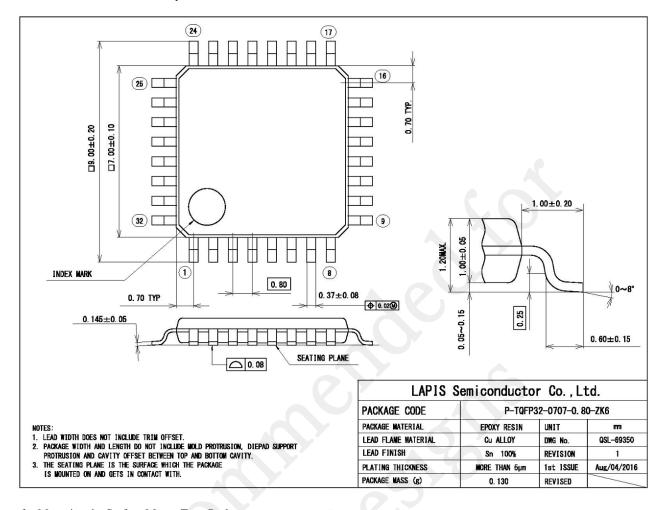

Package Dimensions B-1

Check List E-1

## **Chapter 1 Overview**

#### 1.Overview

#### 1.1 Features

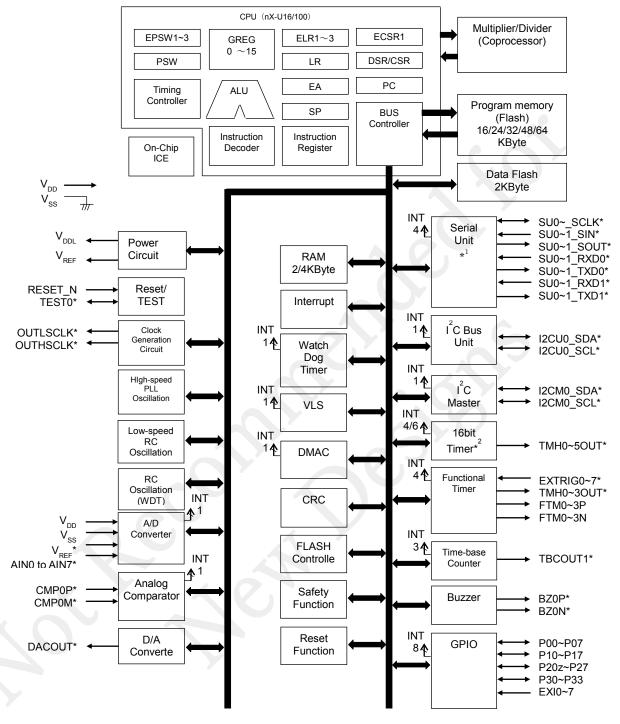

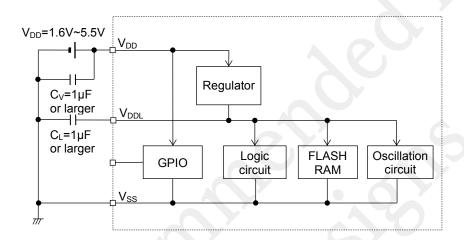

ML62Q1200A Group is a high performance CMOS 16-bit microcontroller equipped with an 16-bit CPU nX-U16/100 and integrated with program memory(Flash memory), data memory(RAM), data Flash and rich peripheral functions such as the multiplier/divider, CRC operator, DMA controller, clock generator, timer, UART, synchronous serial port, I<sup>2</sup>C bus interface unit, buzzer, Voltage Level Supervisor(VSL), successive approximation type A/D converter, D/A converter , analog comparator, safety function and etc.

The CPU nX-U16/100 is capable of efficient instruction execution in 1-intruction 1-clock mode by pipeline architecture parallel processing.

The built-in on-chip debug function enables debugging and programming the software. Also, ISP(In-System Programming) function supports the Flash programming in production line.

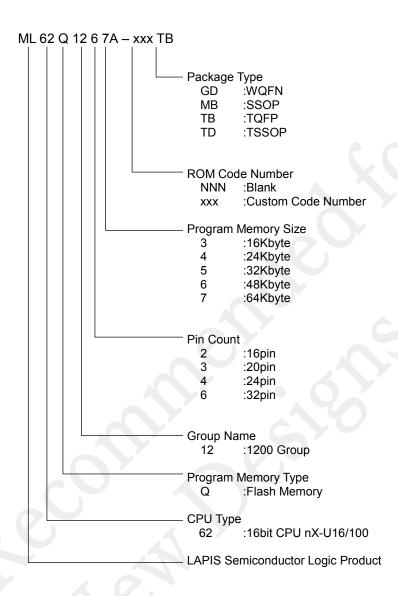

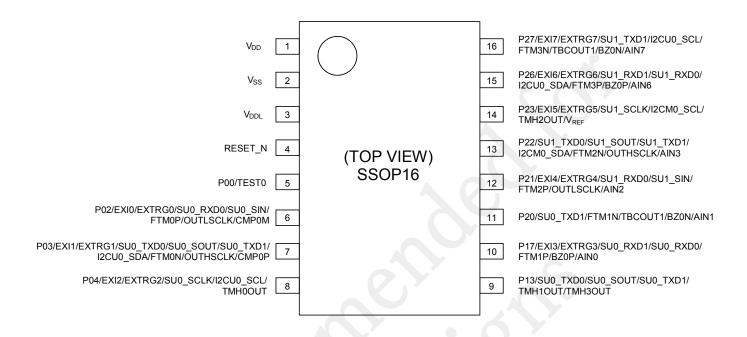

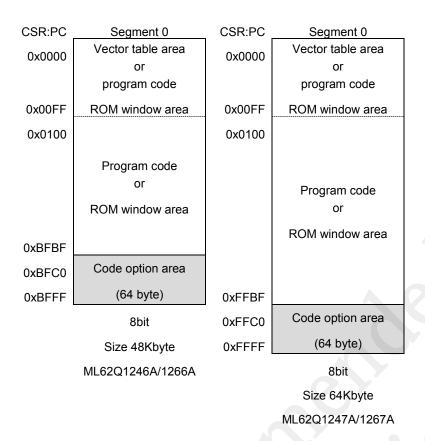

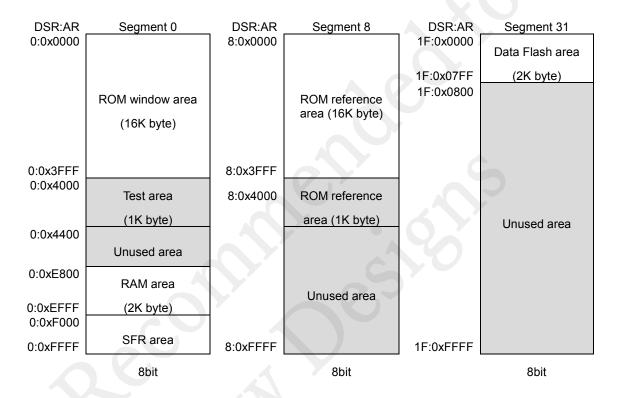

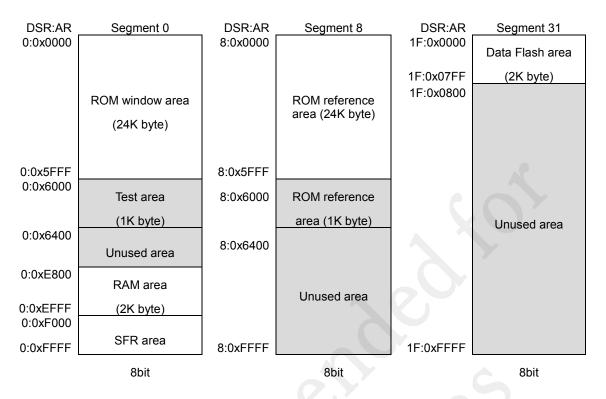

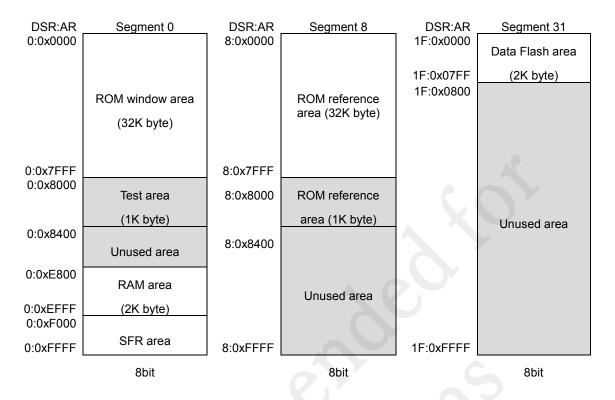

The ML620Q1200A Group has five packages (16pin - 32pin) and five kinds of memory sizes(16Kbyte - 64Kbyte).

|                   |                      | Table 1 1 WE | -,                        |                  |                 |                 |

|-------------------|----------------------|--------------|---------------------------|------------------|-----------------|-----------------|

| Program<br>memory | Data memory<br>(RAM) | Data Flash   | 16pin<br>SSOP16<br>WQFN16 | 20pin<br>TSSOP20 | 24pin<br>WQFN24 | 32pin<br>TQFP32 |

| 64Kbyte           | 4Kbyte               | 2Kbyte       | _                         | -                | ML62Q1247A      | ML62Q1267A      |

| 48Kbyte           | 4Kbyte               | 2Kbyte       | _                         | _                | ML62Q1246A      | ML62Q1266A      |

| 22Kbyto           | 4Kbyte               | 2Kbyte       | -                         | _                | ML62Q1245A      | ML62Q1265A      |

| 32Kbyte           | 2Kbyte               | 2Kbyte       | ML62Q1225A                | ML62Q1235A       |                 | _               |

| 24Kbyte           | 2Kbyte               | 2Kbyte       | ML62Q1224A                | ML62Q1234A       | <u> </u>        | _               |

| 16Kbyte           | 2Kbyte               | 2Kbyte       | ML62Q1223A                | ML62Q1233A       | A 3             | _               |

Table 1-1 ML62Q1200A Group Product List

#### • CPU

- 16-bit RISC CPU (CPU name: nX-U16/100)

- Instruction system: 16-bit length instruction

- Instruction set: Transfer, arithmetic operations, comparison, logic operations, multiplication/division, bit manipulations, bit logic operations, jump, conditional jump, call return stack manipulations, arithmetic shift, and so on

- On-chip debug function built-in (supported by LAPIS on-chip debug emulator EASE1000)

- ISP (In-System Programming) function built-in

- Minimum instruction execution time 30.5 μs (at 32.768 KHz system clock)

62.5ns/41.6ns (at 16 MHz/24MHz system clock)

- Coprocessor for multiplication and division

- Multiplication: 16bit × 16bit (operation time 4 cycles)

- Division: 32bit / 16bit (operation time 8 cycles)

- Division: 32bit / 32bit (operation time 16 cycles)

- Multiply-accumulate (non-saturating): 16bit × 16bit + 32bit (operation time 4 cycles)

- Multiply-accumulate (saturating): 16bit × 16bit + 32bit (operation time 4 cycles)

- Operating voltage and temperature

- Operating voltage: VDD = 1.6 to 5.5 V

- Operating temperature: -40 to 105 °C

#### • Internal memory

Prrogram Flash memory area Rewrite count: 100 cycles Rewrite unit: 32bit(4byte)

Erase unit: 16Kbyte/1Kbyte

Erase/Rewrite temperature: 0°C to +40°C

Data Flash memory area

Rewrite count 10,000 cycles

Rewrite unit: 8bit(1byte)

Erase unit: 2Kbyte/128byte

Erase/Rewrite temperature: -40°C to +85°C

Back Ground Operation(CPU can work while erasing and rewriting)

#### - Data RAM area

Rewrite unit: 8bit/16bit(1byte/2byte)

Parity check function (Parity error reset is generatable)

#### Clock

Low-speed clock

Internal low-speed RC oscillation (32.768 KHz)

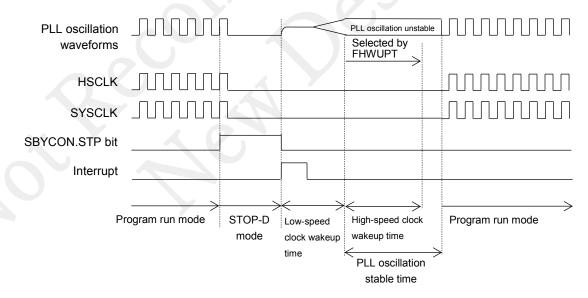

High-speed clock

PLL oscillation (32MHz/24MHz/16MHz is selectable by flash code option)

WDT(Watch Dog Timer) independent clock Internal low-speed RC oscillation (1kHz)

#### Reset

- RESET N pin reset

- Reset by power-on detection

- Reset by the 2<sup>nd</sup> watchdog timer (WDT) overflow

- Reset by counter clear during the windows close of watchdog timer (WDT)

- Reset by RAM parity error

- Reset by voltage level detection (VLS)

- Reset by invalid memory access (detecting abnormal program counter)

- The software reset by BRK instruction (reset CPU only)

#### Power management

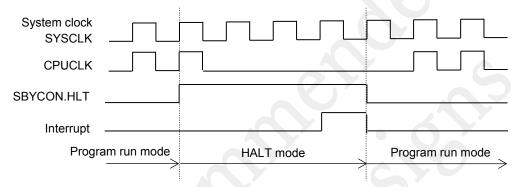

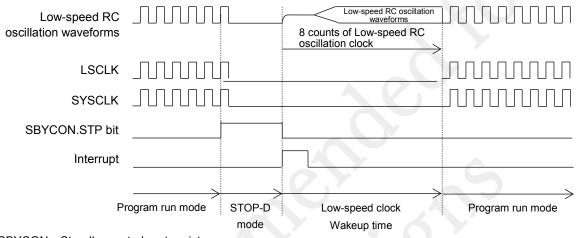

- HALT mode: CPU stops executing instruction, clock oscillations and peripheral circuits remain previous states

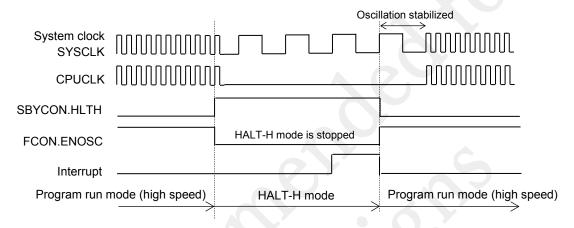

- HALT-H mode: CPU stops executing instruction, high-speed clock oscillation stops and peripheral circuits working with low-speed clock remain previous states

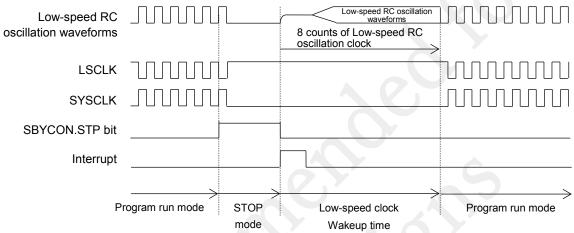

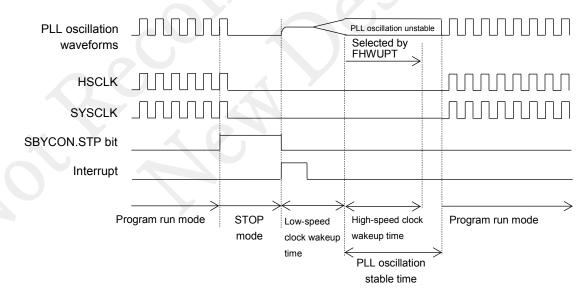

- STOP mode: CPU stops executing instruction, both high-speed oscillation and low-speed oscillation stop.

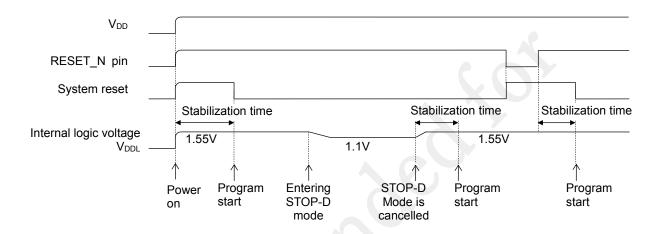

- STOP-D mode: CPU stops executing instruction, both high-speed oscillation and low-speed oscillation stop. The

internal regulator's output voltage (V<sub>DDL</sub>) goes down to reduce the current consumption (RAM data are

retained).

- Clock gear: The frequency of high-speed system clock can be changed by software (1/1, 1/2, 1/4, 1/8, 1/16 or 1/32 of the oscillation clock)

- Block Control Function: Powers down the circuits of unused function blocks (reset the block or stop supplying the clock)

#### • Interrupt controller

- Non-maskable interrupt source: 1 (Internal sources: WDT)

- Maskable interrupt sources: max.31 (ML62Q126xA/32pin: Internal sources: max.23, External sources: 8)

Four step interrupt levels

- Watchdog timer(WDT)

- Operation clock: 1kHz WDT independent clock or 32.768kHz RC oscillation clock, selectable by code option

- Overflow period: 8 types selectable (8ms, 16ms, 32ms, 64ms, 125ms, 500ms, 2000ms and 8000ms @32.768kHz)

- WDT counter clear enable period : 50%, 75% or 100% of overflow period

When 100% of overflow period is selected,

The first overflow generates an interrupt, and the second overflow generates a reset.

When 50% or 70% of overflow period is selected,

The first overflow generates a reset.

Clearing the WDT counter out of the enable period generates the WDT invalid clear reset.

- WDT operation: Enable or disable is selectable by code option

- Readable WDT counter (WDT counter monitor function)

#### • DMA(Direct Memory Access) controller

Operation mode : Wait mode

- Channel: 2ch

- Transfer unit: 8bit/16bit

Max. transfer count: 1024 time

- Transfer type: 2 cycle transfer

- Transfer mode: Single transfer mode

Fixed address, address increments and address decrements

- Transfer target: SFR/RAM ←→ SFR/RAM (Transfer from/to Flash is not supported)

- Transfer request: Serial unit interrupt, A/D interrupt and Timer interrupt

#### • Time base counter

- Devide the Low-speed clock(LSCLK) and generate 32.768kHz~1Hz internal pulse signals

- Priodical interrupt × 3 selectable from 8 frequencies (128Hz, 64Hz, 32Hz, 16Hz, 8Hz, 4Hz, 2Hz and 1Hz)

- The time base clock output (1Hz or 2Hz) from general purpose ports (TBCOUT1).

#### • Functional timer(FTM)

- Channel: 4ch

- Timer one shot mode and repeat mode, Caputure mode, PWM mode1 and PWM mode2(complementary output)

- Same start/stop is avaible with different channels

- (This function is not avaible with 16bit Genral Timer)

- Event trigger (external interrupts, analog comprator interrupts, 16bit genral timer interrupts and Functional timer interrupts)

- Delay counter (for generating dead time for motor control)

- Available to specify devision ratio of counter clock channel by channel

#### • 16bit General timers

- Channel: 6ch

- 8 bits timer mode and 16-bit timer mode (1ch 16-bit timer is configurable as 2ch 8-bit timer)

- Same start/stop is avaible with different channels

- (This function is not avaible with Functional Timer)

- Timer output (toggled by overflow)

- Available to specify devision ratio of counter clock channel by channel

- Serial communication unit

- Channel: Max. 2ch

- Synchronous Serial Port or UART is seletable in each channel

- < Synchronous Serial Port >

- Master/slave selectable

- LSB first/MSB first selectable

- 8-bit length/16-bit length selectable

- < UART >

- Full-duplex communication x 2 ch(One Full-duplexUART is configurable as two half-duplex UARTs)