#### Dear customer

ROHM Co., Ltd. ("ROHM"), on the 1st day of April, 2024, has absorbed into merger with 100%-owned subsidiary of LAPIS Technology Co., Ltd.

Therefore, all references to "LAPIS Technology Co., Ltd.", "LAPIS Technology" and/or "LAPIS" in this document shall be replaced with "ROHM Co., Ltd." Furthermore, there are no changes to the documents relating to our products other than the company name, the company trademark, logo, etc.

Thank you for your understanding.

ROHM Co., Ltd. April 1, 2024

# RB-D610Q338TB52 User's Manual

Issue Date: January 13, 2022

#### Notes

- 1) The information contained herein is subject to change without notice.

- 2) When using LAPIS Technology Products, refer to the latest product information (data sheets, user's manuals, application notes, etc.), and ensure that usage conditions (absolute maximum ratings, recommended operating conditions, etc.) are within the ranges specified. LAPIS Technology disclaims any and all liability for any malfunctions, failure or accident arising out of or in connection with the use of LAPIS Technology Products outside of such usage conditions specified ranges, or without observing precautions. Even if it is used within such usage conditions specified ranges, semiconductors can break down and malfunction due to various factors. Therefore, in order to prevent personal injury, fire or the other damage from break down or malfunction of LAPIS Technology Products, please take safety at your own risk measures such as complying with the derating characteristics, implementing redundant and fire prevention designs, and utilizing backups and fail-safe procedures. You are responsible for evaluating the safety of the final products or systems manufactured by you.

- 3) Descriptions of circuits, software and other related information in this document are provided only to illustrate the standard operation of semiconductor products and application examples. You are fully responsible for the incorporation or any other use of the circuits, software, and information in the design of your product or system. And the peripheral conditions must be taken into account when designing circuits for mass production. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising from the use of these circuits, software, and other related information.

- 4) No license, expressly or implied, is granted hereby under any intellectual property rights or other rights of LAPIS Technology or any third party with respect to LAPIS Technology Products or the information contained in this document (including but not limited to, the Product data, drawings, charts, programs, algorithms, and application examples, etc.). Therefore LAPIS Technology shall have no responsibility whatsoever for any dispute, concerning such rights owned by third parties, arising out of the use of such technical information.

- 5) The Products are intended for use in general electronic equipment (AV/OA devices, communication, consumer systems, gaming/entertainment sets, etc.) as well as the applications indicated in this document. For use of our Products in applications requiring a high degree of reliability (as exemplified below), please be sure to contact a LAPIS Technology representative and must obtain written agreement: transportation equipment (cars, ships, trains, etc.), primary communication equipment, traffic lights, fire/crime prevention, safety equipment, medical systems, servers, solar cells, and power transmission systems, etc. LAPIS Technology disclaims any and all liability for any losses and damages incurred by you or third parties arising by using the Product for purposes not intended by us. Do not use our Products in applications requiring extremely high reliability, such as aerospace equipment, nuclear power control systems, and submarine repeaters, etc.

- 6) The Products specified in this document are not designed to be radiation tolerant.

- 7) LAPIS Technology has used reasonable care to ensure the accuracy of the information contained in this document. However, LAPIS Technology does not warrant that such information is error-free and LAPIS Technology shall have no responsibility for any damages arising from any inaccuracy or misprint of such information.

- 8) Please use the Products in accordance with any applicable environmental laws and regulations, such as the RoHS Directive. LAPIS Technology shall have no responsibility for any damages or losses resulting non-compliance with any applicable laws or regulations.

- 9) When providing our Products and technologies contained in this document to other countries, you must abide by the procedures and provisions stipulated in all applicable export laws and regulations, including without limitation the US Export Administration Regulations and the Foreign Exchange and Foreign Trade Act.

- 10) Please contact a ROHM sales office if you have any questions regarding the information contained in this document or LAPIS Technology's Products.

- 11) This document, in part or in whole, may not be reprinted or reproduced without prior consent of LAPIS Technology.

(Note) "LAPIS Technology" as used in this document means LAPIS Technology Co., Ltd.

Copyright 2022 LAPIS Technology Co., Ltd.

i

## LAPIS Technology Co., Ltd.

2-4-8 Shinyokohama, Kouhoku-ku, Yokohama 222-8575, Japan https://www.lapis-tech.com/en/

## **Table of Contents**

| Οve  | erview                                                                                                          | .1                                                                                                                                                                                                                                                      |

|------|-----------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Оре  | erational notes                                                                                                 | .1                                                                                                                                                                                                                                                      |

|      |                                                                                                                 |                                                                                                                                                                                                                                                         |

|      |                                                                                                                 |                                                                                                                                                                                                                                                         |

|      |                                                                                                                 |                                                                                                                                                                                                                                                         |

| -    |                                                                                                                 |                                                                                                                                                                                                                                                         |

| 5.2. |                                                                                                                 |                                                                                                                                                                                                                                                         |

| 5.3. |                                                                                                                 |                                                                                                                                                                                                                                                         |

| 5.4. |                                                                                                                 |                                                                                                                                                                                                                                                         |

| 5.5. |                                                                                                                 |                                                                                                                                                                                                                                                         |

| 5.6. |                                                                                                                 |                                                                                                                                                                                                                                                         |

| 5.7. |                                                                                                                 |                                                                                                                                                                                                                                                         |

| PCI  |                                                                                                                 |                                                                                                                                                                                                                                                         |

|      |                                                                                                                 |                                                                                                                                                                                                                                                         |

| 3.2. |                                                                                                                 |                                                                                                                                                                                                                                                         |

|      |                                                                                                                 |                                                                                                                                                                                                                                                         |

|      |                                                                                                                 |                                                                                                                                                                                                                                                         |

|      | Ope<br>Han<br>Boa<br>Spe<br>5.1.<br>5.2.<br>5.3.<br>6.4.<br>5.5.<br>6.6.<br>5.7.<br>PCI<br>3.1.<br>3.2.<br>3.3. | 5.2. LED(P22-P24)         5.3. ADC(AIN4-AIN7)         5.4. Jack         5.5. CN1 Connector         5.6. CN2 Connector         5.7. CNE connector         PCB specification, BOM list and Schematic         5.1. PCB specification         5.2. BOM list |

#### 1. Overview

This instruction manual is for the RB-D610Q338TB52 which is the reference board for ML610Q338 (hereinafter referred to as "MCU") that is 8-bit microcontroller with voice output function.

This board can be combined with on-chip debug tool EASE1000 V2 and software development environment(DUT8 and MWU16) to do the following:

- Development and debugging of the MCU control software.

- Programing control and sound code data to the MCU internal Flash-ROM.

- Voice playback by the MCU.

#### 2. Operational notes

The following describes the precautions to follow when handling the RB-D610Q338TB52.

- Turn off the power when inserting and removing jumper socket from PWR/SPVDD/VREF Jumper pin on the RB-D610Q338TB52.

- Turn off the power when attaching and deattaching external board, device and cable from CN1/CN2/CNE Connector on the RB-D610Q338TB52.

- Connect only monaural speakers to the jack on the RB-D610Q338TB52.

- RB-D610Q338TB52 is a device used only by experts in R&D facilities for research and development purposes. RB-D610Q338TB52 is not intended to be used in mass-produced products or parts thereof.

- The information in this document is subject to change without notice due to product improvement and technological improvement. Prior to use, please ensure that the information is up to date.

- LAPIS Technology does not provide any RB-D610Q338TB52 support. Replace only in case of initial failure.

## 3. Hardware specifications

Table 1 shows the hardware specifications of RB-D610Q338TB52. For more information about the connection of the mounted components, see the schematic.

Table 1 Hardware specifications

| Manueladici                      | . 11. M. (100229 52 TOED                                                               |  |  |  |  |

|----------------------------------|----------------------------------------------------------------------------------------|--|--|--|--|

| Mounted LSI                      | • U1: ML610Q338 52pin TQFP                                                             |  |  |  |  |

|                                  | • PWR(J1): Jumper for selecting the power supply input (3pin pin-header and short pin) |  |  |  |  |

|                                  | • VREF(J2): Jumper for selecting VREF(3pin pin-header and short pin)                   |  |  |  |  |

|                                  | • SPVDD(J3): Jumper for selecting SPVDD(3pin pin-header and short pin)                 |  |  |  |  |

|                                  | • C1-C4: Capacitors for Powers                                                         |  |  |  |  |

| Other Mounted                    | • P22-P24: LEDs                                                                        |  |  |  |  |

| components                       | • R1-R3: Resistors for LEDs                                                            |  |  |  |  |

|                                  | • R4-R6: Jumper Chip for connecting LEDs                                               |  |  |  |  |

|                                  | <ul> <li>R7-R10: Resistors for Successive Approximation Type A-D Converter</li> </ul>  |  |  |  |  |

|                                  | JACK: Jack for connecting Speakers                                                     |  |  |  |  |

|                                  | • CNE: Connector for EASE1000 V2(14pin connector)                                      |  |  |  |  |

| Pads (or/and)                    | <ul> <li>C5-C8: Capacitors for Successive Approximation Type A-D Converter</li> </ul>  |  |  |  |  |

| Through holes for                | • CN1-CN2: Connectors for user application system (32pin, 2.54mm pitch, φ0.8mm )       |  |  |  |  |

| mounting components              | • SP1: Land for ferrite beads(1608)                                                    |  |  |  |  |

| Power check pins/pads            | · VDD, SPVDD, UVDD, USPVDD, VSS, SPVSS, AIN4-AIN7 (φ0.8mm)                             |  |  |  |  |

| Operating voltage                | • +2.0~+5.5V                                                                           |  |  |  |  |

| Board size • 55.88 mm x 93.98 mm |                                                                                        |  |  |  |  |

## 4. Board Outline Diagram

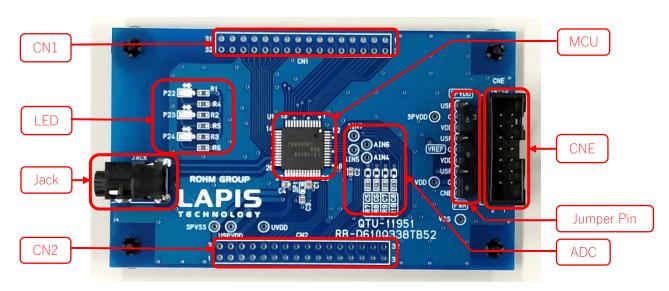

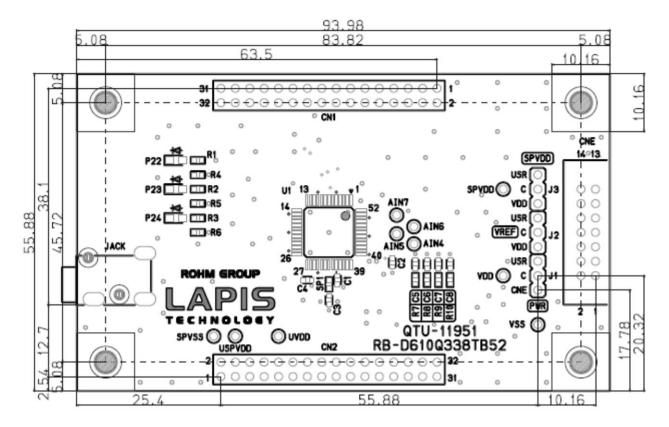

Figure 1 shows an outline diagram of the RB-D610Q338TB52.

Figure 1 Board Outline Diagram

## 5. Specification

#### 5.1. Power Circuit

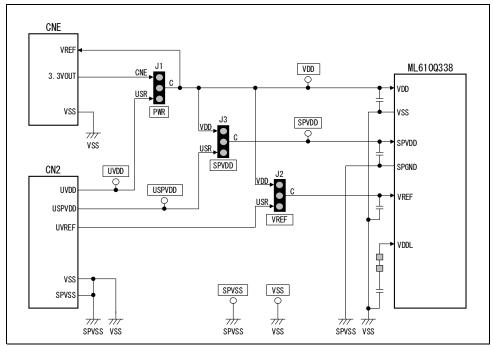

Figure 2 shows a power curcuit of the RB-D610Q338TB52. The RB-D610Q338TB52 has junper pins that can switch the supply source of the VDD / VREF / SPVDD pins of MCU. Each is explained below.

Figure 2 Power circuit

#### •PWR jumper pin(J1)

PWR jumper pin can switch the supply source of VDD pin of MCU.

| PWR | Contents                                    |  |  |  |  |

|-----|---------------------------------------------|--|--|--|--|

| CNE | VDD pin is connected to 13pin of CNE.       |  |  |  |  |

| USR | VDD pin is connected to 9pin (UVDD) of CN2. |  |  |  |  |

When attaching "EASE1000 V2" on the board, PWR jumper pin set to "EASE" if power supply from 13pin of CNE connector. PWR jumper pin set to "USR" if power supply from CN1 connector.

#### VREF jumper pin(J2)

VREF jumper pin can switch the supply source of VREF pin of MCU.

| VREF | Contents                                         |  |  |  |  |

|------|--------------------------------------------------|--|--|--|--|

| VDD  | VREF pin is connected to 2pin of PWR jumper pin. |  |  |  |  |

| USR  | VREF pin is connected to 19pin (UVREF) of CN2.   |  |  |  |  |

VREF jumper pin set to "VDD" if power supply from VDD as same as selecting PWR jumper pin. VREF jumper pin set to "USR" if power supply from CN2 connector.

#### •SPVDD jumper pin(J3)

SPVDD jumper pin can switch the supply source of SPVDD pin of MCU.

| SPVDD | Contents                                           |  |  |  |  |

|-------|----------------------------------------------------|--|--|--|--|

| VDD   | SPVDD pin is connected to 2pin of PWR jumper pin.  |  |  |  |  |

| USR   | SPVDD pin is connected to 3/4pins (USPVDD) of CN2. |  |  |  |  |

SPVDD jumper pin set to "VDD" if power supply from VDD as same as selecting PWR jumper pin. SPVDD jumper pin set to "USR" if power supply from CN1 connector.

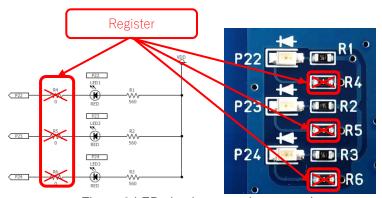

#### 5.2. LED(P22-P24)

P22-24 pins of MCU on the RB-D610Q338TB52 allow direct LEDs drive. Enable to use LEDs connecting these pins when the N-channel open drain output is selected. Unmount register on the board indicated by "R4-R6" when not using LEDs. Figure 3 shows the LED circuit processing example.

Figure 3 LED circuit processing example

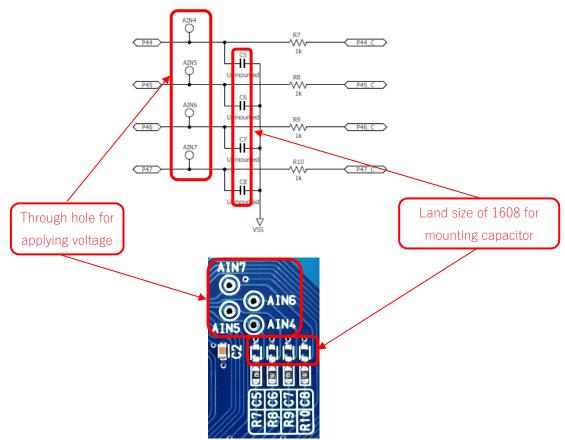

#### 5.3. ADC(AIN4-AIN7)

The RB-D610Q338TB52 has registers indicated by "R7-R10" and capacitors indicated by "C5-C8" (not mounted) so that P44-P47 pins of MCU are enable to use as AIN4-AIN7 which are Succesive Approximation type A-D Converter functions. Mount a noise reduciton capacitor on board land indicated by "C5-C8" if necessary. Figure 4 shows the ADC circuit processing example.

When using the Succesive Approximation type A-D Converter functions without using resistors, apply a voltage to the through hole.

Figure 4 ADC circuit processing example

#### 5.4. Jack

Jack is connnected to SPP/SPM pins of the MCU. Connect only monaural speakers to the jack.

#### 5.5. CN1 Connector

The through holes indicated by "CN1" are enable to mount connector that specification is double row, 16 positions and 2.54mm(0.1mil) pich.

Table 2 shows a CN1 connector pin assignment.

Table 2 CN1 connector pin assignment

| CN1        |             | Connected to | Damanda  |         |

|------------|-------------|--------------|----------|---------|

| Pin number | Part Symbol | Number       | Pin name | Remarks |

| 1          | U1          | 1            | P93      |         |

| 2          | -           | -            | -        |         |

| 3          | U1          | 2            | P80/EXI0 |         |

| 4          | U1          | 3            | P81/EXI1 |         |

| 5          | U1          | 4            | P20/LED0 |         |

| 6          | U1          | 5            | P21/LED1 |         |

| 7          | U1          | 6            | P22/LED2 |         |

| 8          | VSS         | -            | VSS      |         |

| 9          | U1          | 8            | P23/LED3 |         |

| 10         | U1          | 9            | P24/LED4 |         |

| 11         | U1          | 10           | P25/LED5 |         |

| 12         | U1          | 11           | P91      |         |

| 13         | -           | -            | -        |         |

| 14         | -           | -            | -        |         |

| 15         | VSS         | -            | VSS      |         |

| 16         | VSS         | -            | VSS      |         |

| 17         | -           | -            | -        |         |

| 18         | -           | -            | -        |         |

| 19         | -           | -            | -        |         |

| 20         | U1          | 14           | PA4      |         |

| 21         | U1          | 15           | P82/EXI2 |         |

| 22         | U1          | 16           | P83/EXI3 |         |

| 23         | U1          | 17           | PA3      |         |

| 24         | U1          | 18           | PA2      |         |

| 25         | U1          | 19           | PA1      |         |

| 26         | U1          | 20           | PA0      |         |

| 27         | U1          | 21           | P90      |         |

| 28         | U1          | 22           | RESET_N  |         |

| 29         | U1          | 23           | SPP      |         |

| 30         | U1          | 24           | SPP      |         |

| 31         | U1          | 25           | SPM      |         |

| 32         | U1          | 26           | SPM      |         |

#### 5.6. CN2 Connector

The through holes indicated by "CN2" are enable to mount connector that specification is double row, 16 positions and 2.54mm(0.1mil) pich.

Table 3 shows a CN2 connector pin assignment.

Table 3 CN2 connector pin assignment

| CN2        |             |        |                 |                 |

|------------|-------------|--------|-----------------|-----------------|

| Pin number | Part Symbol | Number | Pin name        | Remarks         |

| 1          | =           |        | SPVSS           |                 |

| 2          | U1          | 28     | SPVSS           |                 |

| 3          | J3          | 3      | USPVDD          | J3:SPVDD jumper |

| 4          | J3          | 3      | USPVDD          | J3:SPVDD jumper |

| 5          | U1          | 31     | P84/EXI4        |                 |

| 6          | U1          | 32     | P92             |                 |

| 7          | VSS         | -      | VSS             |                 |

| 8          | VSS         | -      | VSS             |                 |

| 9          | J1          | 3      | UVDD            | J1:PWR jumper   |

| 10         | U1          | 36     | PB0             |                 |

| 11         | U1          | 37     | PB1/TIA0A       |                 |

| 12         | U1          | 38     | PB2/TIA0C       |                 |

| 13         | U1          | 39     | PB3             |                 |

| 14         | -           | -      | -               |                 |

| 15         | -           | -      | -               |                 |

| 16         | -           | -      | -               |                 |

| 17         | -           | -      | -               |                 |

| 18         | -           | -      | -               |                 |

| 19         | J2          | 3      | UVREF           | J2:VREF jumper  |

| 20         | U1          | 41     | P40/AIN0/HPC0   |                 |

| 21         | U1          | 42     | P41/AIN1/HPC1   |                 |

| 22         | U1          | 43     | P42/AIN2/TIAOUT |                 |

| 23         | U1          | 44     | P43/AIN3        |                 |

| 24         | U1          | 45     | P44/AIN4        |                 |

| 25         | U1          | 46     | P45/AIN5        |                 |

| 26         | U1          | 47     | P46/AIN6        |                 |

| 27         | U1          | 48     | P47/AIN7        |                 |

| 28         | U1          | 49     | P85/EXI5        |                 |

| 29         | U1          | 50     | P86/EXI6        |                 |

| 30         | U1          | 51     | P87/EXI7        |                 |

| 31         | U1          | 52     | PC0             |                 |

| 32         | -           | -      | -               |                 |

#### 5.7. CNE connector

CNE connector is used to connect the on-chip debug tool EASE1000 V2 manufactured by LAPIS Technology Co., Ltd. Refer to the "EASE1000 V2 User's Manual" for details.

## 6. PCB specification, BOM list and Schematic

### 6.1. PCB specification

Figure 5 shows the PCB dimensional outline diagram and layout of components.

Figure 5 PCB dimensional outline diagram and layout of components (Top view)

#### 6.2. BOM list

#### Table 4 BOM list

|    | Parts Number        | Symbol                  | Contents                      | Qty. | Vendor                     |

|----|---------------------|-------------------------|-------------------------------|------|----------------------------|

| 1  | QTU-11951           | RB-D610Q338TB52         | PWB                           | 1    | LAPIS Technology Co., Ltd. |

| 2  | C1608X7R1E105K080AB | C1,C2,C3,C4             | Ceramic Capacitor 1uF/25V X7R | 4    | TDK                        |

| 3  | -                   | C5,C6,C7,C8             | Unmounted                     | 4    | -                          |

| 4  | -                   | CN1,CN2                 | Unmounted                     | 2    | -                          |

| 5  | HIF3FC-14PA-2.54DSA | CNE                     | 14pin Header                  | 1    | HIROSE                     |

| 6  | MJ-354A0            | JACK                    | Monaural Speaker Jack         | 1    | MARUSHIN                   |

| 7  | SML-M13UT           | LED1,LED2,LED3          | LED Red                       | 3    | ROHM                       |

| 8  | MCR03EZPJ561        | R1,R2,R3                | Resistor 560Ω ±5%             | 3    | ROHM                       |

| 9  | MCR03EZRJ000        | R4,R5,R6                | Resistor 0Ω                   | 3    | ROHM                       |

| 10 | MCR03EZPJ102        | R7,R8,R9,R10            | Resistor 1kΩ ±5%              | 4    | ROHM                       |

| 11 | A2-3PA-2.54DSA(71)  | J1,J2,J3                | 3pin Header                   | 3    | HIROSE                     |

| 12 | HIF-3GA-2.54SP      | -                       | Jumper Socket                 | 3    | HIROSE                     |

| 13 | -                   | TP1,TP2,TP3,TP4,TP5,TP6 | Unmounted                     | 6    | -                          |

| 14 | -                   | AIN4,AIN5,AIN6,AIN7     | Unmounted                     | 4    | -                          |

| 15 | ML610Q338-NNNTB     | U1                      | MCU                           | 1    | LAPIS Technology Co., Ltd. |

| 16 | FF013-P3555-AR791   | -                       | Rubber leg, Push rivet        | 4    | KOYO FASTENER              |

#### [Note]

- The diameter of through hole of CN1 and CN2 is 0.8mm.

Using CN1 and CN2, the diameter of connector pin should use the connector below 0.8mm, such as 0.5mm.

- The parts may be changed into another parts with equivalent part special quality.

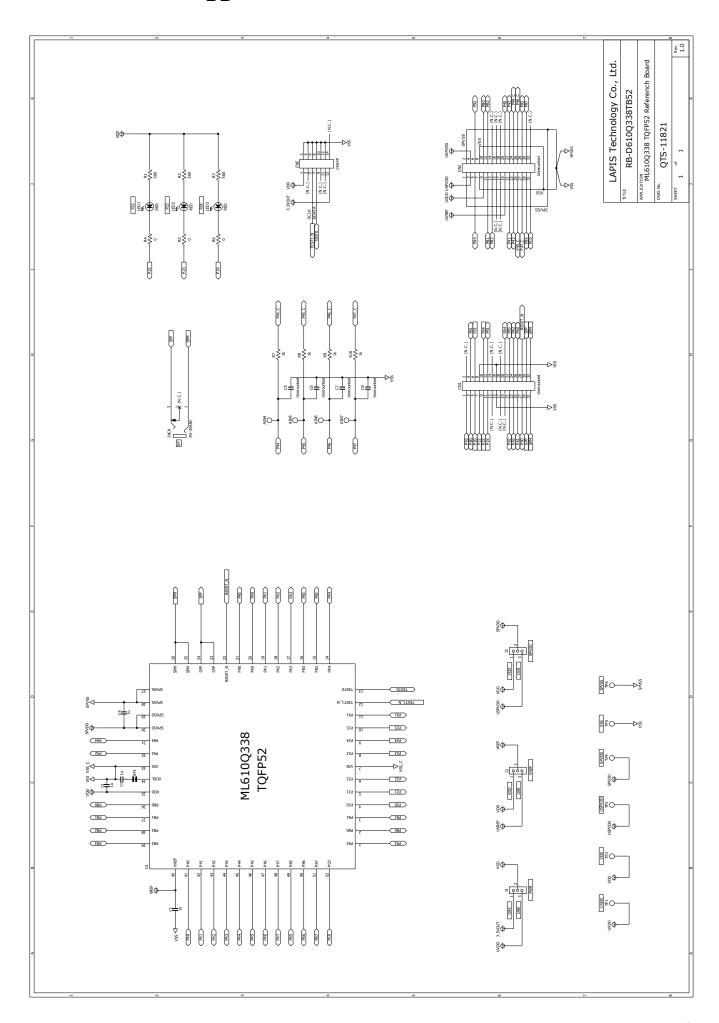

#### 6.3. Schematic

The schematic of RB-D610Q338TB52 is shown below.

# 7. Revision History

|                  |              | Page                |                |                |  |

|------------------|--------------|---------------------|----------------|----------------|--|

| Document No.     | Issue Date   | Previous<br>Edition | New<br>Edition | Description    |  |

| FJBL610Q338RB-01 | Jan 13, 2022 | -                   | -              | First edition. |  |